引言

现代雷达对频率合成器相位噪声、快速捷变能力、灵活多变的波形产生、带内杂散提出越来越高的要求。全相参直接式频率合成器具有较高的频率稳定度,短的跳频时间,直接式频率合成器的缺点是杂散抑制,而且设备量庞大。锁相频率合成器的缺点在于如果环路总分频比太大,会严重恶化输出的相位噪声;且频率变换速度较慢。所以将直接倍频与数字锁相结合,利用开关的快速切换速度、直接倍频的频率稳定性、数字锁相的灵活多变,完成方案的设计。

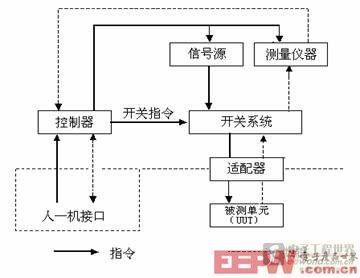

系统框图

当数字锁相环间歇工作(数字锁相环只用于频率捕获)时,数字锁相环锁定时间需要40~50ms。这是由于在数字锁相环停止工作期间环路滤波器输出电压总是处于饱和状态,当数字锁相环重新工作时必须经历一段较长的恢复时间才能正常工作。数字锁相环的频率捕获时间过长是它的缺点,但是它的数字接口灵活易变,一条环可完成多个稳定频率点的需求,相应的设备量少。电子开关的速度为nS级,可完成快速捷变的需求。在频率控制时稍加设计,就可将两者的优点有效的结合起来。当开关由第一条环选向第二条环时,第二条环已在上一个时钟稳定,捷变时间由开关决定;同时,第一条环由数字界面控制,改变频率。如此类推,下一个时钟时,当开关由第二条环选向第一条环时,第一条环已在上一个时钟稳定,捷变时间由开关决定。由此,很好的解决了直接倍频的难点—杂散抑制。xa0xa0xa0xa0

再由倍频器展宽频带。

X波段上变频器是杂散信号的主要来源,因其是宽带混频,通带内会出现交调分量,这里采取两项措施解决,一项措施是计算好混频器的输入信号(fi)和输入本振信号(fL),使

APP下载

APP下载 登录

登录

热门文章

热门文章