我在一个高大上的公司做工程师的时候并不知道这个关系式,直到我后来卖示波器才知道有这么一个关系式,而且很重要。再追溯到我读书的时候,当然更不知道这个关系式。

做工程师的时候,我的老板告诉我,为了确保示波器能准确地捕获电源MOS管的峰值电压,千万不要在屏幕上同时看很多波形,尽量让示波器上只显示一个脉冲。他的做法是不断地调节触发电平,肉眼盯着示波器看,直到他调节触发电平到足够高(多少是足够?),认为某次“抓到”的峰值电压应该就是最大的了。 他为什么不同时捕获更多的波形,只要确保采样率是最大或者足够就好了,再打开参数测量的统计值不是更好吗? 但是他只相信自己的眼睛盯着看到的那个波形,并断定某一个波形就一定是最大的了。还好他会使用触发电平的。我们小弟当然也就相信他是权威啦,因为他当时确实已经是公司级的专家了。……

这个真实故事给了我要举办1000场示波器技术交流会的强大理由。工程师们不太愿意拿出1个小时听听示波器的基础课程,总觉得这示波器很简单,但其实对于示波器的ABC的认知还是太少。有些人将这个作为中国工程师和国外工程师的区别之一。这个判断多少是令人有点愤怒的,但确实在某种程度上真的是这样。 甚至换一个角度说,一个公司使用示波器的专业程度基本能反应一个公司的研发水平的。

那么今天我们花一点点时间快速阅读一下这篇关于示波器存储深度的“浅浅的”文章吧。为满足大家快阅读的需求,先将文章的标题摘录如下:

1,存储深度的基本概念

2,示波器存储器的物理介质

3,存储深度和采样率的关系

4,最大存储深度,当前设置的最大存储深度,存储深度的叠加使用,可显示的存储深度,可分析存储深度,

5,存储深度的应用价值

------------------------------------------------------------------------------------------------------

存储深度被称为示波器的第三大指标。存储深度=采样率*采样时间。这个关系式被笔者称为示波器的第一关系式。

1,存储深度的基本概念

“存储深度”是个翻译过来的词语,英文叫“Record Length”。有的将它翻译成“存储长度”,“记录长度”,等。它表示示波器可以保存的采样点的个数。存储深度是“1千万个采样点”,示波器厂商写作10Mpts,10MS或10M的都有。这里,pts可以理解为points的缩写,S理解为Samples的意思。

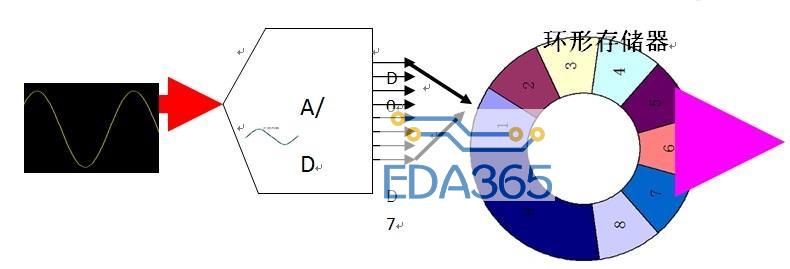

存储深度表现在物理介质上其实是某种存储器的容量,存储器英文就是“Memory”。该存储器容量的大小也就是“存储深度”。存储器保存满了,达到存储深度的极限之后怎么办? 我们可以将示波器的存储器理解为环形存储器。示波器不断采样得到新的采样点会填充进来,老的采样点会自动地溢出,这样周而复始的过程直到示波器被“触发信号”“叫停”或者间隔一定长的时间被强迫“叫停”为止。“叫停”一次,示波器就将存储器中保存的这些采样点“搬移”到示波器的屏幕上显示。这两次“搬移”之间等待的时间相对于采样的时间极其漫长,被称为“死区时间”。

上述过程经常被笔者这样打比方:存储器就像一个“水缸”,“水缸”的容量就是“存储深度”。如果使用一个“水龙头”以恒定的速度对水缸注水,水龙头的水流速度就是“采样率”。当水缸已经被注满水之后,水龙头仍然在对水缸注水,水缸里的水有一部分会溢出来,但水缸的总体容量是保持不变的。在某种条件下,水缸里的水将被全部倒出来,周而复始。图1形象地表示了这种环形存储器的概念。

图1 示波器的环形存储器

2,示波器存储器的物理介质

存储器的物理介质是什么? 是否就是我们熟悉的DDR内存呢? 容量为什么那么小?为什么不可以用硬盘或者SD卡等大容量介质作为物理介质呢? 如果是硬盘作为存储介质,示波器不就可以作为数据记录仪了吗?

回答上述问题其实并不容易!

据笔者了解,早期的示波器包括现在的高带宽示波器使用的存储器都是示波器厂商自己设计的专用芯片,甚至一度存储器芯片和ADC芯片之间的配合是A公司(后来叫K公司)的一个技术瓶颈。在若干年之前,K公司的所有示波器在存储深度达到每通道2Mpts采样点之后,采样率会自动降低到4GS/s,直到2006年(好象是这个年份,也许更晚点),当年的A公司收购了某芯片公司才解决这个技术瓶颈。现在K公司的低带宽示波器的所有系列中,存储深度指标一直不能突破每通道2Mpts,我猜想它可能采用的还是老款芯片。

对于高端示波器,存储器芯片一直是核心技术,对于里面的技术细节笔者知之甚少。示波器中的ADC速率太快,普通的存储介质根本来不及在这么短的时间内“吞吐”那么大量的数据量。

还是用具体的数字来理解高速ADC的超大数据量对存储器“吞吐量”提出的要求。譬如ADC的采样率是20GS/s,也就是说每秒钟要采样20G个点,而每个点是由8个0和1组成。如果ADC的输出是完全按照串行数据的传输到存储器中,那么传输速率就是160Gbps。这是什么概念? 现在的PCI-Express 3.0的速率是 8Gbps,最高速的高速芯片在单板上传输速率能达到25Gbps,但还不成熟,也没有用到示波器上。高速ADC的采样点怎么传输到存储器中,这是一个难题! 其实这么高速的ADC也不可能是单芯片设计的,内部是由很多2.5GS/s或1.25GS/s,250MS/s的“小的”ADC“交织拼接”实现的。既然不完全是串行的方式实现,采用并行传输之后,传输到存储器的数据又怎么校准、对齐,再通过触发机制规整地显示到示波器屏幕上呢? 这是示波器厂商的一点点小秘密。示波器发展到今天这方面门槛谈不上多高,但还是有那么一点点的。

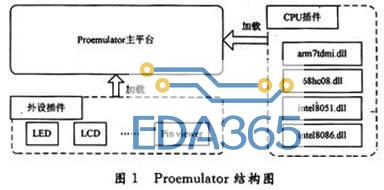

大家可能又会问另外一个问题,存储器的数据又是怎么传输CPU中被分析、被显示呢? 这也是一个问题,这问题涉及到示波器的数据处理的架构。随着示波器技术的发展,目前存在的两种架构,一种是基于PC平台的,另外一种是嵌入式的,主要是基于FPGA实现的。随着DDR内存速率的提高和FPGA计算能力的增强,现在基于FPGA计算平台的存储器芯片已经不再神秘,多是采用工业上的DDR内存颗粒了,因此存储深度这个指标,在不顾及存储的采样点是否真的被显示、被分析的情况下,可以做得特别大了。但往往真实情况是,虽然存储深度很高,但显示的采样点数和分析的采样点数可能只有千分之几,这主要取决于FPGA的“计算资源”或者说取决于成本,换句话说,取决于示波器产品的定义了。当然在不顾及成本的情况下,可以向外行人吹嘘一下是算法的优势。在这类产品中,在屏幕上看到的波形对应的存储深度并不等于采样率乘以采样时间,这有时侯确是让人很纠结的。

3,存储深度和采样率的关系

存储深度=采样率*采样时间。笔者一直执着地将它称为示波器中的第一关系式,因为很多工程师在使用示波器过程中因为忘记这个关系式而产生错误。如图2为中国首款智能示波器SDS3000的显示界面。右下方红色方框中,右边两个数值50MS/s和20ms/div相乘,再乘以10,就等于左边的数10MS。当前采样率为50MS/s,当前时基为20ms/div,因为水平轴是10格(有些示波器是12格或14格),因此采样时间为200ms, 50MS/s * 200ms = 10MS。就是说以50MS/s的采样率捕获200ms的波形,需要示波器的存储幅度是10MS。这和水缸里面注水是一个概念,如果“水龙头”的流速是每秒5千万(50M)滴水,那么持续向“水缸”注水200ms,水缸中就有了1千万(10M)滴水了。 就是这么简单的乘积关系。

APP下载

APP下载 登录

登录

热门文章

热门文章