网络、多媒体、移动通信对提高数据吞吐率的需求与日俱增,推动计算机和通信技术不断突破速度极限。图1是当前主流计算机外设总线的速率演变情况。

图1主流高速串行标准演进图

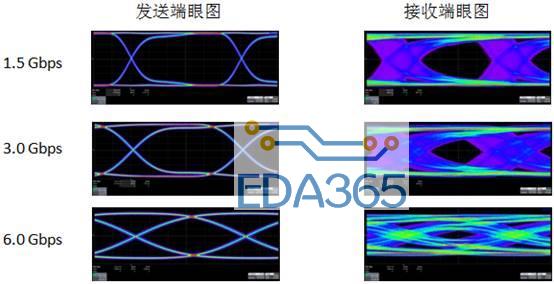

数据率越高,信道趋肤效应和介质损耗对信号质量的影响越严重,在时域上表现为:边沿变缓,码间干扰加剧,抖动增加。通常使用眼图来评估高速信号质量。下图是三种速率的信号在发送端和接收端分别测得的眼图。可以明显看出,速率越高,接收端的眼图闭合程度越小。能否在接收端正确检测出受损的信号,是高速收发器芯片设计者面临的挑战。

图2不同速率信号的失真程度

在以往的高速串行信号一致性测试标准里,一般都要求测试发送端性能,比如输出电压摆幅、上升时间、抖动、眼图等。随着速率提高,仅仅测试信号发送端已经不能保证高速链路能按预期性能正常工作,必须对接收机性能也进行测试。USB 3.0、PCI Express 3.0以及SATA和SAS规范已经明确要求进行接收机测试。

2.接收机测试原理

在发送器测试中,通常利用示波器直接测量输出信号的幅度、上升/下降时间、眼图和抖动,从而评估发送器的驱动能力、预加重、参考时钟稳定性等各项性能。在接收端,典型的接收机芯片框图如下:

图3典型接收机内部框图

它包含

信号检测(放大,均衡)

基于锁相环(PLL)的时钟恢复

判决电路(并转串,线路码解码)

对接收机性能的测试实际就是对以上三个主要部件的性能测试:

1)可以识别出多小幅度的信号,即接收灵敏度

2)时钟恢复电路中的锁相环能否去除低频抖动

3)能够正确识别出带有多大抖动的数据,即抖动容限

不像发送端可以直接测量被测件(Device Under Test,DUT)输出的信号,信号进入接收机内部后无法直接观测,一般使用仪器产生一定样本量、一定特征的激励数据流给DUT。这些特征一般是多种形式的“干扰”,仪器通过施加不同程度的“干扰”,测试接收机的表现。

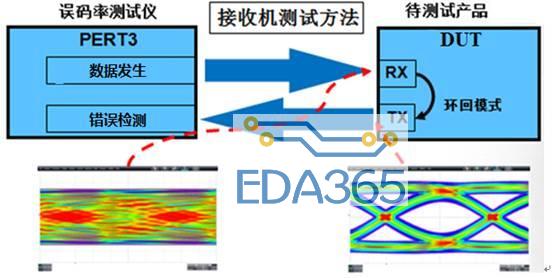

这种仪器一般是误码率测试仪(Bit Error Rate Tester,BERT)。简单的说,误码率测试就是发送已知数据给被测接收机芯片,通过量化被错误判决数据的比例来衡量接收机芯片的性能。在功能上,误码率测试仪包括数据发生(Pattern Gernerter)和错误检测(Error Detetor)两个部分,即前者产生激励,后者检测响应。

图4误码率测试仪工作原理框图

测试时,误码率测试仪和DUT收发互连形成回环,如图5。Pattern Generator发出带有“干扰”的信号给DUT。DUT将接收到的数据经过内部回环又发送回给误码率测试仪。一般经过DUT内部的检测和时钟域变换,发送回去的数据不再带有“干扰”。

图5误码率测试仪与DUT回环连接

DUT一般有两种回环模式:

1)外部BERT(或称Retimed Loopback)

图6外部BERT测试框图

DUT将RX端收到的BERT数据从TX端发送回去,由BERT对比发送和接收到的数据

APP下载

APP下载 登录

登录

热门文章

热门文章