等有时间从内到外系统详细的说说示波器的构造原理,就知道为啥那么贵了.

现在开始,我感觉关注这个问题的都是硬件相关的人,所以讲的比较具体,闲麻烦可以只看每段的最后一句话:

首先,做硬件,几千上万都便宜的很了。。。要讲示波器为啥那么贵,就要介绍一下示波器,在介绍示波器之前,就要先了解一下示波器是用来干什么的,当然是用来测波形的,,,这里,波形我们可以人为的分为两类:高速信号和低速信号(具体怎么分析信号,另一个话题了,很庞大)。

我们计划买一台示波器的时候,首先应该是从需求出发,即我们想要测什么样的波形。这里就引出了整个信号设计及验证过程中最重要的一个概念:带宽。也就是我们平时在不停BB的,这个信号是多少M的多少G的频率(频率!不是带宽!),这个示波器的几G的带宽。

那么,我们怎么把信号的频率和示波器的带宽对应起来呢?比如如我们要测一个5GHz频率方波的数字信号,我们需要买一台具体多大带宽,多大采样率的示波器呢?有人会说,3倍,3.5倍... 都不对!不要死记,要懂原理,需要看你具体要测的信号,和想要测到信号的几次谐波。如果想测到3次谐波:15G带宽,5次谐波:25G带宽,7次,9次,,,。这里的带宽指的就是奈奎斯特频率。

引出了这个奈奎斯特频率的概念之后,我们就可以先围着这个讲一下示波器的大致结构了:

我们从信号的整个处理流程讲各部分原理:传输(到探头),衰减,放大,低通滤波(可能放在放大或衰减前一步做,看具体方案),硬件触发(软件触发会放在采样之后),采样,运算(包括CDR),输出到屏幕。这里最贵的,就是这个“采样”部分,也就是我们说的AD;接着就是“低通滤波”,滤波器根据不同示波器的种类会有不同的滤波类型(放在后面讲);再接着就是“衰减”和“放大”(为什么要先衰减了信号,还要再放大,放在后面讲)和运算,其他的相比之下,都可以理解为不值钱,,,

接下来,我们要根据信号处理流程,从后往前慢慢详细具体讲一台33GHz带宽100GSaps的示波器的大致结构和原理:

1, 运算和显示:信号经过AD之后,每个采样点都变成了一个8bit(或12bit)的整型数据,这些点的数据一般都是从ADC直接经过DMA dump到DRAM里的,这里需要高速大带宽低延迟的内部互联方式---高位宽并行接口(可能每个ADC到DMA的接口都要128bit甚至更高),当这一大坨的数据放到ram里之后,就可以不需要实时的来处理了(当然不会delay很大,信号触发了10s了,波形还没显示出来,就没有用户体验了。所谓不实时就是可以串行处理或者分块分批了),接下来一般是放在ASIC(或FPGA)里做处理运算,是不会用到你听过的普通cpu的(i9设计出来不是给你处理大数据的,,,)。这里处理主要是要做插值和按照你选的套件或者measure类型去做一些运算,比如CDR之后出个眼图,卡个信号幅值或频率之类的,然后整堆的数据会直接再次通过DMA送给Graphics显示到屏幕。这里值钱的部分是FPGA(ASIC),这个稍微高端一点的,国内做不出来,并且可以预料在很长一段时间内都做不出来,而且大多数情况下,所使用的ASIC量都很少,流一次片的成本或多或少大家都听过,也就可以想象每个ASIC能贵到什么程度了。

2, ADC:ADC是最简单的,但是世界上能做出来高端ADC的一共就那么几家。前端处理完的信号,到了ADC,经过AD之后,变成了一大堆的数字信号就完了。这里,高速的AD,一般就是通过时分的方法,并列使用,串行采样。就比如,有两个10GSaps的ADC,每个ADC采样一次的间隔是0.1ns,那么当第一个ADC采样完成之后,间隔0.05ns第二个ADC开始采样,输出数字信号进行合并,这里就相当于我有了一个20GSaps的ADC。一般采样频率到了百G的ADC都应该是这类使用方式。这里会有一个想问题,就是即使ADC芯片做的一致性极好,Vbias做的也是一样,但是由于是分立的die,就还是会出现采样值会有误差。如果有高速示波器和更高速的信号发生器,可以去试一下,一个标准的正弦波经过一个同带宽的示波器之后会有幅值失真。所以这类方法虽然很好解决了高速采样的问题,但是也不会使用多个ADC并列。一般可能会是2个。这个ADC以及ADC直间时延调整,只有卖示波器的厂能做的出来。每个卖示波器的厂都是从做ADC开始的,贵的原因同样就是设计难,还不外销,量极少。

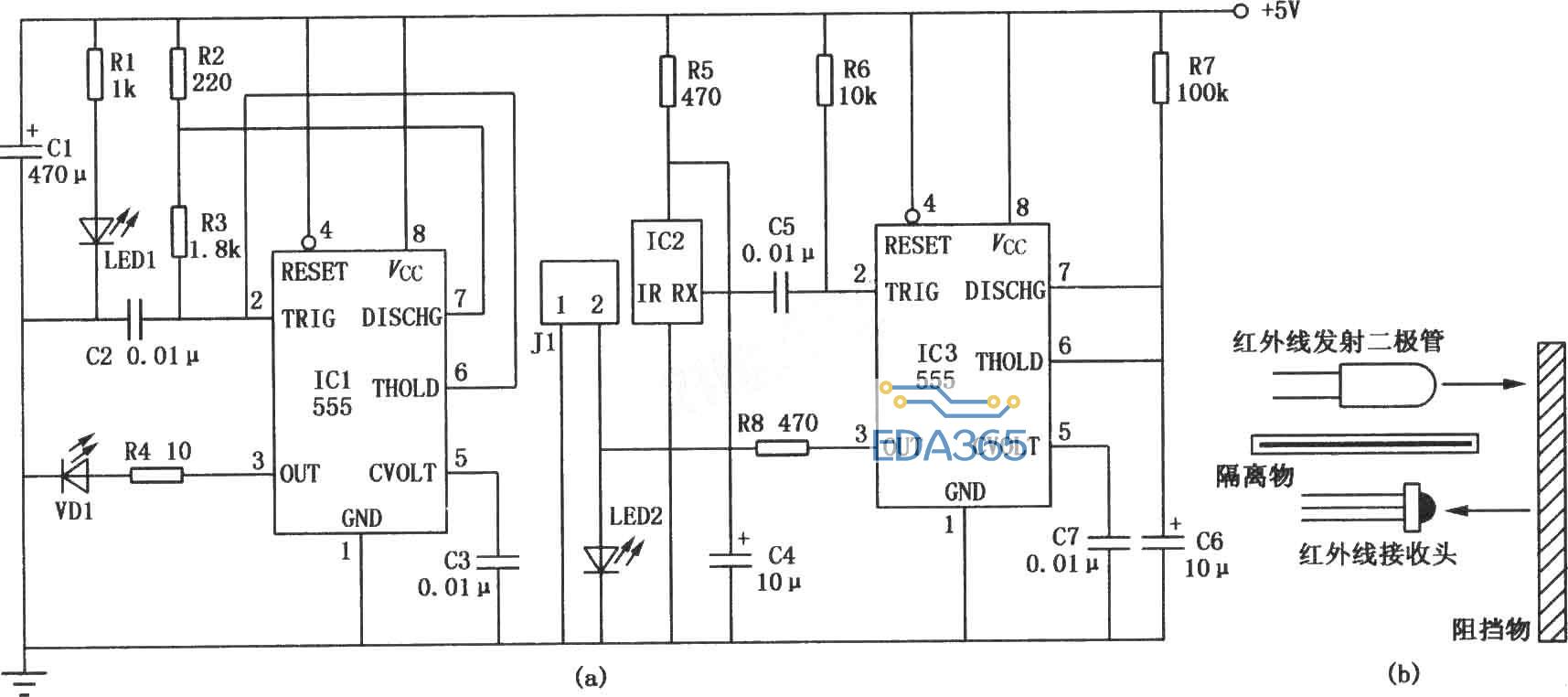

3, 硬件触发:早些时候的示波器是软件触发的,这样,信号只有采样采到了想要的Trigger状态才会触发。因为信号不是连续一直采样的,所以触发的命中率做不到100%。现在增加了硬件触发电路,类似于比较器+DAC之类的东西,就可以先触发在采样。不过相比其他,这部分电路成本就很低了。

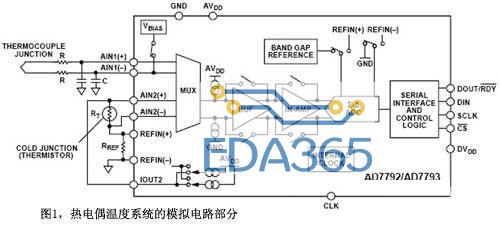

4, 低通滤波:首先要知道为什么需要有低通滤波器。还记得前面讲过的奈奎斯特频率嘛,如果一个信号不经过低通就直接送进了ADC,如果这个信号的频率已经大于了奈奎斯特频率,那么AD之后的波形就已经出现了混叠现象,也就失真了。所以需要将输入信号的3dB带宽限制在奈奎斯特频率以内。根据示波器种类的不一,前端低通滤波器响应曲线一般有两种:实时示波器使用Maximally Flat Respones和采样示波器使用Bessel Response。具体这两中频响曲线的异同优缺点不细说。这个滤波器要有好看的频响曲线,还要有可控的Groupe Delay,是狠精密的,难实现的,算法都是公开,拓扑结构也是写在课本里的,但是国内就是做不出来,即使你买来别人的示波器打开抄,高速的前端都抄不来性能做不出来的东西当然贵。还有一个小问题,最新的高端示波器(>60GHz 带宽)对中国是禁运的。此处应该贴上赵本山:不卖!多少钱不卖!那个图,但是要严肃,,,不过高速示波器有中国特供版,带宽阉割到59GHz。。。

5, 衰减和放大:这个相对来讲,要容易一些,这个不是垄断,而且可以买到IP。先衰减的目的是衰减底噪,然后奈奎斯特频率范围内再进行多级放大。这个也是目前国内完全做不出来的,并且可以预料,很长一段时间内也做不出来,想想手机之类的射频AP,也就是刚刚开始的阶段,何况几十GHz的小信号AP呢。但是可以买到(不被制裁的情况下),也就是成本可控了。

6,探头前端:这个可以算作也可以不算做示波器本体,有的时候我们可能不用前端。无源探头很便宜,但是带宽都很低。有缘探头除了要做阻抗匹配意外,可能也会包括一部分的滤波放大电路,目的是保证信号经过一大段探头的cable之后质量可控。这个东西成本可能很低,但是配套出售,一个匹配的电阻都卖几百刀,还是耗材。

示波器几个大部分到这里就都介绍了个大概,前面这6项,除了6#,任何一个带宽上G的示波器,国内这些组件都做不出来,就能想象为什么贵了吧。

目前市场上高速示波器基本价格就是10W rmb/GHz BW,也就是想买个13G的示波器,带点套件,探头,200W。

但是回头想想,不管花了几百万,买来的整个东西全进口,包括壳子布袋之类的附件,没有一样made in China,还贵嘛(狗头)?

整篇回答纯个人根据几年的工作经验和知识积累总结的,我认为必要的点都标了黑体,感兴趣的可以去Google一下这些名词,会收获颇丰的。另外本篇可能会有错误,欢迎指正。

附上一段其他人的解释:

I'd firstly agree with other posters as to economics of scale. Consumer devices are produced in the millions whereas such a market does not exist for digital oscilloscopes.

Secondly, oscilloscopes are precision devices. They need to undergo rigorous quality control to ensure they live up to expected standards. This further increases costs.

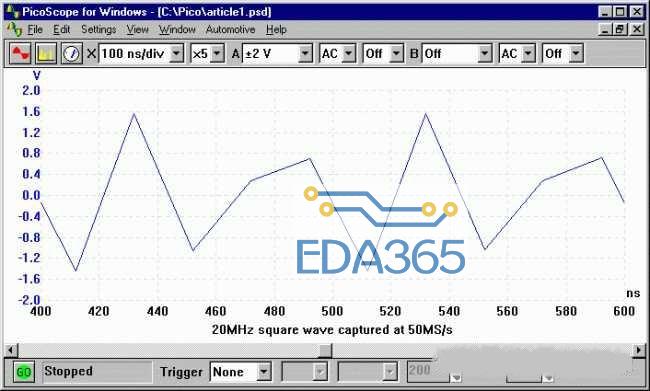

As for bandwidth. The Nyquist criterion states that the sampling rate should be at least twice the frequency you want to measure. But even at twice the rate, it is terrible at best. Consider the following pictures:

The graph captions tell the story. You need to exceed the specified bandwidth by a great amount in order to gain an accurate representation of the square wave input signal (high frequency harmonics). And greater bandwidth = greater cost.

In the end the precision, bandwidth and limited production quantities that drive up prices.

BR.

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多