0 引言

短波通信具有通信距离远、机动灵活、成本低廉等优点,而且是一种抗毁性较强的通信方式,因此在多种领域得到了广泛的应用。随着跳频和自适应等新技术的发展,短波通信的性能也得到进一步的提高。但由于短波信道的特点,一方面,其存在多普勒频移和多径效应,严重影响短波通信的系统性能,特别是对于短波数据传输系统,往往达不到较高传输速率;另一方面,其频率资源有限,易受干扰和窃听,再加上短波通信所使用的媒介,造成短波通信是一个时变、衰落信道,保持良好的通信效果有较高难度。美国Sanders公司推出一种相关跳频电台采用的差分跳频技术在短波信道上实现了跳速为5000hop/s,传输速率最低为2400bps,最高可达19200bps的指标,这在传统的跳频系统中是很难实现的。采用差分跳频技术不仅改变了短波电台由于信道带宽窄、空中信道时变多径特性而导致的低速率数据传输的局面,而且极大地提高了抗跟踪干扰的能力,代表了新一代短波通信技术的发展方向。考虑到使用FPGA器件进行数字系统设计,不仅可以简化设计过程,而且可以降低整个系统的体积和成本,增加系统的可靠性,本文对短波差分跳频信号的发生器进行基于FPGA的整体设计。

1 G函数算法原理

差分跳频系统的关键技术在于G函数的实现。差分跳频G函数的特点是利用跳频频率的相关性来携带待发送的数据信息,同时所产生的频率序列具有良好的随机性和均匀性。常规的G函数表达式为:

式(1)是利用前后跳频Fn,Fn-1之间的相关性来携带数据信息Dn,如图1所示。另一种G函数算法是由前一跳的频率、m序列和数据信息Dn来决定当前的频率值Fn,如图2所示,其数学表达式为:

G是一个特定的函数,由它决定差分跳频的算法。由此可见,m序列控制的G函数算法在相邻跳变频率之间通过数据序列建立了一定的相关性,亦即相邻频率的相关性携带了待发送的数据信息,Dn可取1~4bits。

例如,当传输的数据信息Dn取2bits时,对Dn编码见表1。

设每跳传输2bits,跳频频点数为N=64时,将频率集K分成4个子集,每个子集包含16个频点,分别为K1:0~15;K2:16~31;K3:32~47;K4:48~63。

m序列控制跳频序列在不同的子集上跳变,控制关系如表2所示。

m序列的两位控制数可以表示为m2m1,则整个频率集肚的跳变规律描述如下:

设传输的数据经编码后为D2D1,当前频点为q,则下一跳频点q’为:

在满足表2控制关系的基础上,如果第刀跳与第n-2跳的频点相同,则放弃当前m序列的控制作用,将跳频子集变换,用(q’+N/4)modN代替q’的值。

2 短波差分跳频系统的信号发生器的设计

2.1 短波差分跳频信号发生器的整体设计

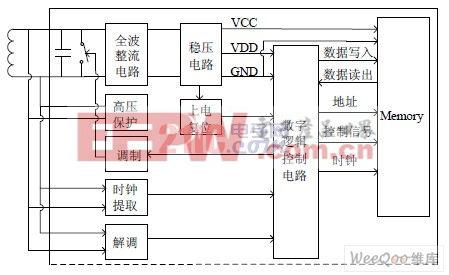

差分跳频信号发生器的功能为根据传输信息数据、前一跳的差分跳频信号频率控制字、m序列和G函数规则产生当前跳的跳频频率控制字,由跳频的频率控制字来控制数字频率合成器,产生对应频率的数字差分跳频信号,最后通过DA转换模块变为模拟差分跳频信号输出。

根据差分跳频信号产生模块的功能,并结合FPGA平台的器件特性,设计的短波差分跳频信号发生器的整体结构如图3所示。

从图3可以看出差分跳频信号发生器共包含6个关键模块:DCM模块、G函数运算模块、频率控制字解析模块、数字频率合成模块、单频数字载波提取模块和DA转换模块。各模块相互协作,共同实现差分跳频系统信号发生器的功能。其中,DCM模块为其他各模块、各单元提供不同的时钟驱动;DA转换模块将数字差分跳频信号变为模拟差分跳频信号输出。其他关键模块的设计将在下一节做详细讲述。

2.2 短波差分跳频信号发生器的关键模块设计

2.2.1 G函数运算模块

G函数运算模块共包括5个功能单元:串并转换单元、m序列产生单元、m序列控制单元、G函数运算单元和G函数校验单元。

串并转换单元对输入数据进行处理,由于数据每次只有1bit输入,因此输入数据经串并转换单元后,可以变为每次传输2bits或4bits数据。

m序列生成单元利用多级线性反馈移位寄存器生成m序列。

m序列控制单元将每次选取m序列的两个最高位作为m序列控制位,控制差分跳频信号频率控制字所在的子集。

G函数运算单元根据G函数规则、m序列的两位控制位、传输的数据信息以及前一跳的跳频频率控制字,产生当前跳的跳频频率控制字。

G函数校验单元判断第n跳和n-2跳的跳频频率控制字是否相同,如果相同,则放弃当前m序列的控制作用,将跳频子集变换,用另一个规则产生当前跳的跳频频率控制字。

2.2.2 数字频率合成模块

数字频率合成子模块共包含8个数字频率合成器,用来产生不同频率的数字载波信号。差分跳频信号产生逻辑控制模块根据差分跳频信号频率控制字产生对应数字频率合成单元的控制信号,为节省输入输出端口,在控制信号和时钟驱动信号的控制下,1个数字频率合成单元产生的不同频率的数字载波信号经过时钟交叠合并为一路数字信号,同时生成一个通道交互信号,差分跳频信号产生逻辑控制子模块根据频率控制字所指定的单一频率的数字载波信号所在通道,按通道交互信号进行单一频率数字载波信号的提取。

2.2.3 频率控制字解析模块和单频数字载波提取模块

频率控制字解析单元在输入时钟的控制下,将频率控制字解析,产生数字频率合成器选择控制信号和通道选择控制信号,同时将通道选择控制信号发送给数字载波信号合并控制单元。数字载波信号合并控制模块通过通道交互信号、数字频率合成模块输出的数字信号和通道选择控制信号,在时钟的驱动下,将数字载波信号合并为一路信号输出。最后将数字信号输出发送给DA转换模块,将其变为模拟信号。

3 短波差分跳频信号发生器的实现

本设计采用XILINX公司推出的型号为XC4VSX35-10FF66的FPGA开发板,利用XILINX公司提供的FPGA开发工具套件,使用Verilog和VHDL两种语言编写完成。

数字频率合成子模块的8个数字频率合成器,每个数字频率合成单元生成8路不同频率的数字载波信号,共可生成64个不同频率的数字载波信号,G函数的频率控制字与差分跳频信号频率对照表如表3所示。

图4为基于FPGA的短波差分跳频信号发生器软件仿真图,最下方的信号为输出的数字差分跳频信号,由仿真时间可以看出每经过200μs输出的差分跳频信号频率发生一次变化,即实现跳速为5000hop/s。图5为数字差分跳频信号经DA转换后变为模拟差分跳频信号的硬件测试结果,其中(a)为示波器显示图,(b)为频谱分析仪显示图。

4 结束语

短波差分跳频通信系统为高速率短波传输提供了一种新的方法。差分跳频体制集调制、解调和跳频图案于一体,是一种特殊的调制解调方式,具有数字化程度高、极易实现高跳速和高数据率、抗跟踪干扰能力强等优点。本文在介绍差分跳频G函数算法原理基础之上,对短波差分跳频信号发生器进行了基于FPGA的整体系统优化设计,并分别在软件和硬件环境下进行了仿真与实现。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多