1双模前置小数分频原理

小数分频器的实现方法很多,但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比,设要进行分频比为K的小数分频,K可表示为:

式中:n,N,X均为正整数;n为到X的位数,即K有n位小数。另一方面,分频比又可以写成:

式中:M为分频器输入脉冲数;P为输出脉冲数。

令P=10n,则:

2电路组成

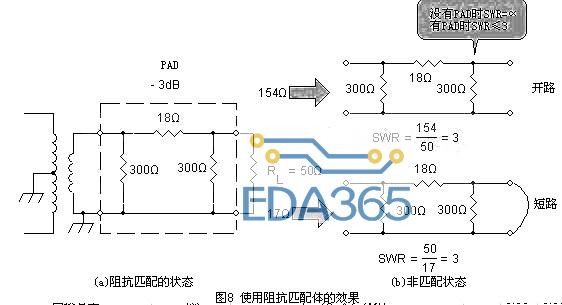

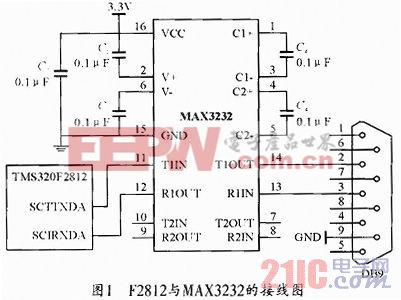

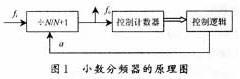

每个周期分频N+10-n.X,其电路双模前置小数分频器电路由÷N/N+1双模分频器、控制计数器和控制逻辑3部分组成。当a点电平为1时,进行÷N分频;当a点电平为0时进行÷N+1分频。适当设计控制逻辑,使在10n个分频周期中分频器有X次进行÷N+1分频,这样,当从fo输出10n个脉冲时,在fi处输入了X.(N+1)+(10n-X).N个脉冲,也就是10n.N+X个脉冲,其原理如图1所示。

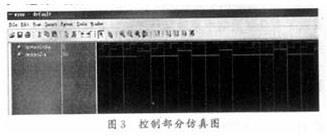

3小数分频器的Verilog-HDL设计

每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。若累加结果小于10,则进行N+1分频,若大于10或等于10,则进行N分频。该例中计数值为(10-7)=3,前3次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,表1给出了该分频器的分频过程。

4波形仿真

上述的÷8/9双模前置分频器的描述程序经ModelSim编译、时序模拟后,得到的波形如图2所示。

由图2可见,当reset为0时,分频器复位,当a为1时,进行8分频,当a为0时则进行9分频。

如图3所示,在前3个时钟,a值为0,则进行9分频,其后一个时钟a为1,进行8分频,后两个脉冲,又进行9分频,后进行一次8分频,然后又进行两次9分频,最后进行一次8分频。

5电路实现

6结语

采用前置双频分频器设计的小数分频器,小数分频器的精度受控制计数器的影响,当n值为100时,小数分频的精度达到1/100;当n值为1000时,小数分频的精度达到1/1000;依此类推。FPGA有相当丰富的硬件资源,因此可以用FPGA设计高精度的小数分频器。采用FPGA组成的数字频率合成器,单环鉴相频率达100MHz以上,分辨率可达10-6。这种小数分频器得到了广泛的应用,例如,对图象采集系统中的行分频和列分频的设计,就可以应用本分频器电路作为时钟发生器。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多