1、 前言

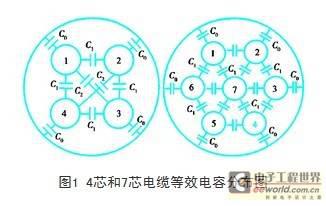

随着嵌入式微机控制技术和现场总线技术的发展,现代列车的过程控制已从集中型的直接数字控制系统发展成为基于网络的分布式控制系统。基于分布式控制的MVB(多功能车辆总线)是IEC61375-1(1999)TCN(列车通信网络国际标准)的推荐方案,它与WTB(绞线式列车总线)构成的列车通讯总线具有实时性强、可靠性高的特点。列车车辆的现代化的发展趋势与可靠性、安全性、通讯实时性的要求使MVB逐渐成为下一代车辆的通讯总线标准。

MVB 是主要用于有互操作性和互换性要求的互联设备之间的串行数据通讯总线,除用于车辆通讯,也可用作其它现场总线。

MVB与MVBC密不可分,MVBC(多功能车辆总线控制器)是MVB总线上的新一代核心处理器,它独立于物理层和功能设备,为在总线上的各个设备提供通讯接口和通讯服务。MVBC与上一代MVB通信控制器BAP15-2/3在性能上有了很大的提高,是目前MVB总线上最先进的通信控制器。

MVB总线通过总线适配器与MVBC相连,根据IEC-61375,MVB总线上采用曼彻斯***,并每64位帧数据后加以8位CRC校验码。MVB的帧分为主帧和从帧,分别由帧头、数据、校验码以及帧尾构成,不同帧的类型通过帧头来判别。

MVB与MVBC之间数据通信在MVBC中由帧收发器来完成,包括帧的发送接收控制、曼彻斯特编解码以及CRC校验码的产生与数据校验。帧收发器在MVBC中起着数据链路层的底层数据处理的作用,是MVBC芯片的设计难点之一,该模块的设计实现对于整个MVBC的开发有着重要的作用。

本文主要介绍位于MVBC总线物理层接口的帧收发器模块的算法和实现方法。

2、 MVBC简介

MVBC可通过配置应用在IEC.TCN标准的Class1,2,3,4设备当中。总线连接可编程车载电子设备,也连接一些简单的传感器及执行机构,最多可寻址4096个设备。

MVBC把来自于MVB总线的串行化信号转换为并行的数据字节,也把需发送的字节交由串行化电路发送到传输介质上。MVBC可根据配置实现总线主与总线从的功能,实现数据链路层以及一部分传输层的数据处理,并通过通讯存储器来与上层软件交互。总线控制器内部包含编码/译码电路和控制通信存储器所需的逻辑电路,用来控制帧的发送和接收(如冲突检测、帧的前导比特处理、CRC校验位的处理等);对输入帧译码并检验其有效性;把数据存放到相应的通信存储器中。

3、 帧收发器的设计

MVBC中的帧收发器主要负责帧的发送、接收,包括曼彻斯***的编码、解码,CRC(循环冗余检测码)的产生与校验,不同类型帧的构建与识别,以及码错的识别和冲突的检测等。其中曼彻斯特编解码以及CRC校验为主要的算法。

3.1 曼彻斯特编码、解码器的设计

MVB总线上的串行数据采用曼彻斯***,曼彻斯特编码中的每个数据位应用以下规范编码:

a)一个“1”的编码在位元的前半部分位“高”,后半部分为“低”;

b)一个“0”的编码在位元的前半部分位“低”,后半部分为“高”;

如图2-4所示:

如果曼彻斯***中出现整个位元的高电平(NH)或整个位元的低电平(NL),则被认为非数据符,用于特殊场合,如:帧头,帧尾标识。 [page]

(1)曼彻斯特编码器

根据曼彻斯***的编码要求,曼彻斯特编码器其电路实现如图2-5所示:

串行数据在1.5M时钟的上升沿处从上一级的移位寄存器输出,在高、低电平时与1.5M时钟相异或,结果得到与上面编码规则相符的曼彻斯***。

(2)曼彻斯特译码器

曼彻斯特译码过程主要是将串行曼彻斯***转变成串行的电平信号,并把串行电平信号组合成并行信号输出,以便进一步处理。如果输入的码字不符合曼彻斯***编码规则(由冲突或其它原因引起),译码器将报告错误信息。

曼彻斯特译码器设计电路如图3-3:

曼彻斯***输入后经过三级寄存器同步,消除亚稳态。如果总线在空闲状态之后出现下降沿,则被认为帧的开始位,总线上再出现高电平时使能16位计数器计数。如果把曼彻斯***每个bit周期分为16个部分,如图3-4:

则在数据采样1处得到的采样值即为曼彻斯特编码前的原数据,数据采样2是用来帧头帧尾检测;总线冲突检测的原则为:总线上曼彻斯***的半个bit周期之内的电平应一致,前后半个周期电平应相异,否则被认为码错。

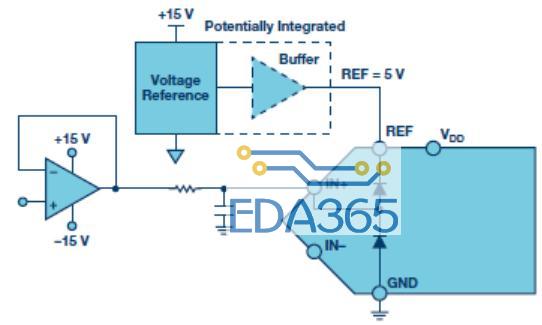

3.2 CRC校验

CRC的全称为Cyclic Redundancy Check,中文名称为循环冗余校验。它是一类重要的线性分组码,编码和解码方法简单,检错和纠错能力强,在通信领域广泛地用于实现差错控制。在各种通信系统中,CRC有bit型算法、字节型算法以及基于查找表的算法。前者适合串行数据通信的校验,后两者常用于高速并行通讯领域。

MVBC可以独立的完成CRC校验码的产生与数据的校验而无需软件参与。其中:

G(x) = x7+x6+x5+x2+1

电路实现方法上我们选择bit型算法,CRC发生电路采用LFSR,主体由一组移位寄存器和模2加法器(异或单元)组成即在数据串行发出的同时,数据经过带有异或单元的移位寄存器产生CRC校验码,实际电路图如图3-5:

串行数据的CRC校验电路也与CRC发生电路一样,不同的是前者CRC电路在移位寄存器之前,而后者在后。 [page]

3.3 总线接口模块的设计实现

总线接口模块包括上述的Encoder、Decoder。

3.3.1 Encoder

Encoder模块主要有以下功能:

(1)构建帧头帧尾;

(2)按照传输层指示进行CRC校验;

(3)对数据进行曼彻斯特编码;

(4)实现主、从帧的发送;

在Class 1 mode以及其它Class mode下,Encoder分别由Class1模块和MCU控制。

如果当前配置允许发送,且控制模块告诉Encoder有帧要发送,以及帧类型、帧长度,则Encoder先将配置好的帧头发送,然后将帧数据、产生的CRC校验码移位后经曼彻斯特编码输出,最后发送帧尾,这样完成主、从帧的发送。电路实现如图3-6所示:

3.3.2 Decoder

MVB总线采用冗余介质,因此MVBC需要冗余的接收模块来完成帧的接收。

(1)两个Decoder根据选择各自完成信号检测(信任线)或冗余检测(冗余线)功能,完成各自帧数据的起始位判定、数据采样、数据解码和数据移位功能;

(2)Decoder从信任线上接收数据,并监视冗余线;

(3)判断帧类型,从帧中提取数据和校验序列(非CRC校验,可选)并存入RXBuffer中;

(4)实现CRC校验,并报告接收状态。

初始化时ICA,ICB分别置为信任线和冗余线(LAA=1),如果信任线超时、寂静,或用户强制,则信任线与监视线互相交换。接收帧的同时,ICA、ICB两个线路上的Decoder将是否接到帧、何种帧类型、接收是否完成、结果对错等信息告诉线路控制模块,该模块将这些信息与哪一个BUFFER有效上报至上层模块进行报文分析。Decoder线路控制图如图3-8:

4、 总线接口模块的验证

验证的思想是通过不同的控制信号,来模拟不同的工作环境下,帧的收发正确性:曼彻斯特编码、帧头、帧尾以及帧数据、帧类型、CRC码的正确性。验证实现结构如图4-1所示:

控制模块将一帧数据写入Txbuffer,并控制Encoder开始发送,此时Encoder发送的帧被Decoder接收;控制模块同时监控Encoder、Decoder的状态,当接收完成后,控制模块将解收到的数据从Rxbuffer读出,从Decoder的接收状态来验证帧的属性:帧是否有效、帧类型、帧长度,并从读出的数据来验证数据的正确性。

5、 结束语

MVB总线伴随着下一代列车通信系统的广泛应用将被普遍采用,同时MVBC也将具有巨大的市场前景。本文主要介绍MVBC与MVB总线接口部分的帧收发器模块的算法分析、设计实现及验证方案。通过作者近期对该模块进行的FPGA验证,充分论证了该设计工作和验证方案的可行性。(end)

热门文章

更多

热门文章

更多