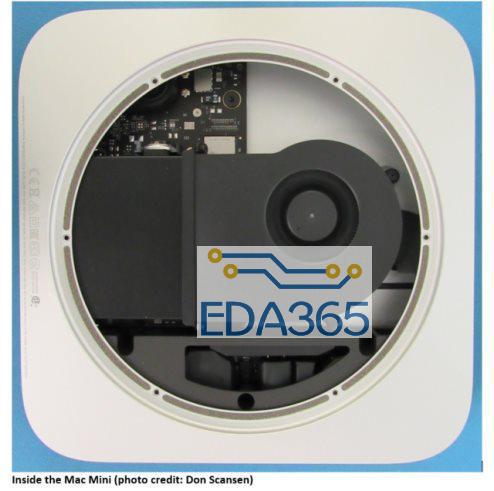

苹果基于ARM架构的自研M1芯片闪亮登场,搭载M1芯片的13寸MacBook Pro、2020款iMac以及Mac mini也悉数亮相。在性能方面苹果自研的M1芯片的确表现不错,目前测试成绩来看,M1在CPU运算方面甚至可以跟英特尔i7、i9相媲美,而GPU方面则直接对GTX 1050Ti进行了压制。为此我们对M1芯片的苹果Mac Mini进行了“解剖”,发现内存和硬盘全都是“焊死”的,跟主板融为一体,但这对于败家高手来说,这不是难事。

先来看看开壳之后的状态,新发布的Macbook Air没有风扇,但Mini可以看到,它似乎只是一个带有强制空气冷却装置的盒子。显然,苹果的想法是以尽可能低的成本制造。

苹果的包装非常艺术,他们好像都是折纸艺术家,他们用纸卡将电源线装在机器下面。这是典型的苹果风。

逻辑主板

从Mac Mini中取出逻辑板并不是什么难事。Mac Mini没有任何伤害或财产损失的风险。组装是精心设计的,并以非常简单的方式分离。打开盒子所需的“防篡改”驱动程序设计为Torx T6H。这是一种内嵌式类型,以便在装配螺丝的中心容纳小柱子。我不知道这是不是故意的,但是有很多常用的精确驱动程序包都包含T7H或更高的值。

拆下螺丝后,逻辑板滑出机箱。四个螺丝将散热器固定在M1和电源管理IC (PMIC)上方。处理器和PMIC都使用翅片散热片,而翅片散热片是由内部风扇进行冷却。正如你在苹果的营销材料中看到的那样,M1处理器被放置在一个封装基板上(球栅阵列- BGA)。这两个DRAM封装没有在散热片范围内。

在BGA基片上有两个并排的LPDDR4 DRAM芯片,位于M1处理器旁边(DRAM端对端放置在处理器硅旁边)。事实上,图像准确地复制了表面安装无源元件的数量、位置和比例。

苹果公司的营销人员还在M1硅的位置放置了一个图像芯片。这显然是不准确的许多原因,但这只是温和的艺术许可。

首先,该设备是附着在BGA上的倒装芯片。这意味着电路面朝下。其次,苹果M1有一个有趣的集成散热器覆盖在Die上。这种薄金属(可能是铝)只覆盖了含有M1硅的BGA衬底的一侧。通常,这些散热装置会覆盖整个包装的顶部表面。

尽管如此,这种带有2D处理器和DRAM的SiP并不常见。

与上代使用Intel处理器中的散热系统不同,这台M1 Mac mini中的散热器是坚固的。我们认为这种新结构的散热效果会更好。主板的背面是一对Texas Instruments USB-C控制器[CD3218B12]。

通用内存架构

最初有人针对M1的拆解是来自16G内存的计算机,它是一对DRAM封装。8G电脑的数量只有一半,有些人怀疑是否只有一个DRAM封装,但事实上8G系统仍然有两个,但每个封装包含的密度是16G组件的一半。Mac Mini的内存是Hynix LPDDR4芯片。

当然,无论系统内存大小,苹果都需要使用两种组件来保持高速RAM芯片的对称性和信号通路。他们并没有考虑为一个计算机平台创建两个封装设计的想法。

这可能是M1设计中最重要的细节。苹果在发布会上强调了新的“通用内存架构”(UMA)。UMA是效率的典范。它允许所有的处理核心CPU和GPU 共享一个大的内存池。保持DRAM物理上的紧密和CPU和GPU核心之间的共享,使得SoC设计可以去掉一些片上SRAM缓存并减少芯片占用空间。

移动处理器使DRAM的距离更加接近。无论是高通的Snapdragon,还是苹果a系列芯片,LPDDR4内存组件都以一种名为package-on-package(PoP)的3D封装概念堆叠在上面。它被认为是更好的方案,可在同一封装体内集成逻辑和存储器件。

看起来M1的内存布局有点退步,但是对于笔记本电脑和台式电脑系统来说,这种设计是必需的。手机和平板电脑处理器的设计理念是让散热更加的优秀,并将PoP的额外热阻也要纳入进去,从而减少芯片外的热传递。非移动计算平台需要有更高的性能,处理器将产生更多的热量。M1模具需要有一个大的表面可以接触散热器。

到目前为止,M1封装的检查只是表面的。虽然配置是有趣的,BGA衬底本身似乎是通用的。但苹果的移动处理器封装和主板级集成一直在挑战边界。也许彻底的创新,隐藏在了盖子底下。

窥探M1内部

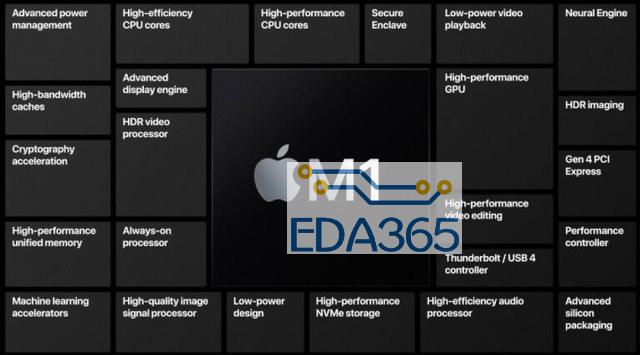

回到苹果硅片上。人们对M1的大部分期待都集中在SoC本身以及设计团队可能带来的成果上。苹果提供了不少线索。功能块插图包括操作细节,其中许多可归因于SoC中的物理IP:

高性能CPU核

高效的CPU核

不间断的处理器

GPU

高带宽SRAM缓存

神经引擎

机器学习加速器

自家Secure enclave技术

加密加速

图像信号处理器

音频处理器

ThunderBolt接口/ USB 4控制器

Gen 4 PCI Express

其中,我们对Thunderbolt控制器最感兴趣。看到两个Intel JHL8040R控制器提供了到两个Thunderbolt 4端口的专用连接。Apple使用了与2018年Intel Mac mini中相同的150W功率的电源控制器。

目前,Thunderbolt设备可与Apple M1 Macs配合良好。

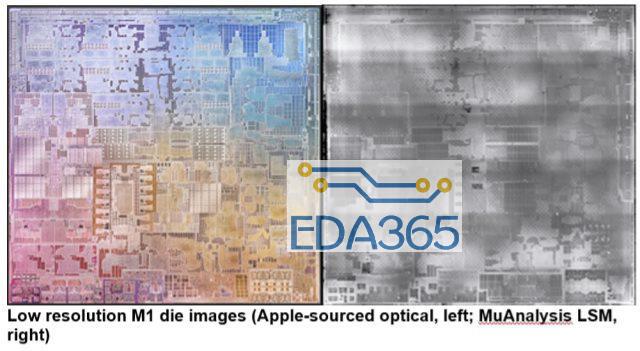

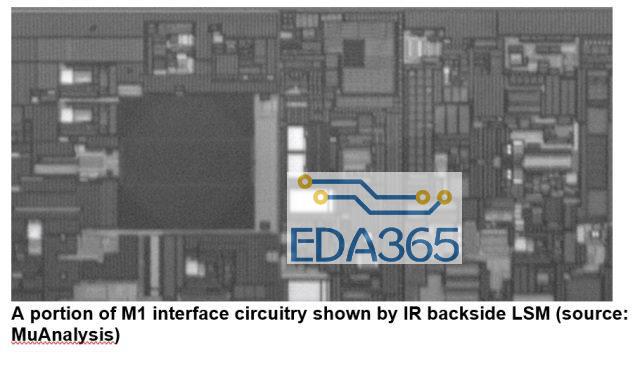

其他方面,苹果没有确定这些模块的芯片位置,即使它被用于描述CPU、GPU和神经引擎的图形暗示。那些插图是程式化的,这说明了它们的不准确性。然而,苹果曾经展示过一些东西,看起来非常像实体产品的SoC模具布局。但这是一种不精确的表示,在某种意义上,它不是真实的组装到封装基板。但它被证明是SoC物理设计的精确版本。

Martine simar - normandin和她的团队使用红外波长的激光扫描显微镜(LSM)通过芯片成像揭示了模具表面的电路模式。硅对红外线IR是透明的,这使得倒装芯片技术得以收益。

在拆解后发现 M1 是标记为 APL1102 的银色芯片,包含了 8 个 CPU 核心,8 个 GPU 核心,16 个神经引擎核心,多个 I/O 主控,所有这些都包含在这个芯片中。统一内存位于芯片的右侧,与以前的Mac mini中使用的独立RAM模块相比,其占用的空间要少得多,从而有助于减小逻辑板的尺寸。

延伸阅读——苹果Secure Enclave为什么很重要?

大家都知道苹果Touch ID会对用户的指纹数据进行加密,并保存在A7芯片内置的 Secure Enclave模块中。而且加密的资料只能直接由处理器存取,无法经由手机硬体取出,苹果对这个技术一直守口如瓶,那么Secure Enclave是什么 ,为什么它很重要?

自从2008年苹果就采用指纹扫描技术,当时很好奇苹果将采取什么样的方式来保护这样重要的生物特征数据,很多砖家当时置疑苹果这个技术的可靠性,直到2012年苹果收购AuthenTec。在支付卡行业工作了30年,又熟悉基本的加密要求,我知道没有软件可以解决这个问题,所以在硬件上必须有一个隔离区来包住这个数据包,它就是苹果的Secure Enclave。

多数手机厂商都模仿了Secure Enclave建立其硬件安全性,三星和谷歌则采取略有不同的方式达到同样的效果。

三星实现了一个物理上不可执行的功能(PUF),在Exynos 9820和9825中充当唯一标识符。谷歌采用了不同的方法,实现了TPM(信任平台模块),将硬件安全模块(HSM)的微型版本焊接到Pixel系列智能手机的PCB上。

Counterpoint的IoT安全服务最新研究数据显示,2019年,嵌入式硬件安全智能手机的销量同比增长39%,基于安全元素的系统占了89%的出货量,而带有PUF的系统占了2019年安全智能手机销量的10%。

Secure Enclave是A系列芯片的特定组成部分,用于存储特别敏感的信息。它用于存储设备密码、人脸识别或Touch ID的生物识别数据,以及Apple Pay数据。至关重要的是,iOS本身无法直接访问安全区域中存储的数据,因此即使恶意软件可以进入iPhone,也无法访问这些数据。

PoP层叠封装

iPhone在2007年亮相,使得层叠封装(PoP)技术又进入了人们的视野。PoP曾经是众人关注的焦点。然而有相当长的一段时间内PoP消失了。目前,更先进的手机将处理器和存储器结合在一起,PoP又成为这类手机的封装选择方案。

如今,所有主要的手机制造商都已转移到PoP结构来,这是带动他们旗舰产品的引擎。其原因不但关系到尺寸和性能――这是直观可见的,而且也关系到商业因素和供应链,虽然这一点并不明显。PoP的未来十分光明,因为很多新产品都正在采用它,这些产品要求性能不断提高,形状因子继续缩小,以及不同的存储器配置和接口。多样的PoP正处于快速发展阶段,以满足不断增加的需求。PoP这种形式已证明了自身的成熟性,那么除手机之外的其他应用也开始受益于PoP的采用。

在封装理念中,将存储器叠层在逻辑器件上看似比较合理,这可以实现更大规模的小型化、性能和成本效益。然而,看似符合逻辑的想法却并非如此简单。因为逻辑处理器是逻辑加存储配置或叠层中价值较高的器件,逻辑器件制造商在将他们的逻辑器件与存储器件集成时遇到很大困难。他们预计购买晶圆形式的存储器,但这并不是他们自身的产品,因此他们对存储器件的测试良率、交互作用和质量非常关心。此外,存储器测试的专业性非常强,最好留给存储器制造商来完成,并可查看测试结果,以免遇到意想不到的复杂性和高成本。经过前期几次倒霉的尝试,大多数想将逻辑与存储器件集成在同一封装体内的逻辑器件制造商都在焦虑地寻找更好的方法。

PoP被认为是更好的方案,可在同一封装体内集成逻辑和存储器件。PoP的底部可容纳逻辑器件,这种封装的底面可以处理高引脚数,要求器件采用微小的焊球间距。PoP的顶部可容纳存储器件或器件叠层。由于存储器件一般要求引脚数较低,可以通过周边阵列来处理,即在两个封装体互连的封装边缘处。封装体的底部可以由逻辑器件制造商来制造和测试――每个都会影响他们核心的能力和技术。在一个封装内集成外来的芯片所造成的责任问题可以消除了,因为每个制造商只负责他们自己的封装。终端用户、手持设备制造商可以通过调配来获利,即传统的存储器供应商来供应顶部封装,逻辑器件供应商来提供底部封装。他们的配置也比较灵活,有多个存储器货源和封装类型,可以与多个处理器封装类型和供应商相匹配。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多