美国半导体研究联盟(SRC)旗下拥有“纳米电子研究创新联盟”(Nanoelectronics Research Initiative;NRI)以及“半导体先进技术研发网路”(Semiconductor Technology Advanced Research Network;STARnet)等组织致力于开发后矽晶时代的下一代技术,这些技术成果还将与IBM、英特尔(Intel)、美光(Micron)与德州仪器(Texas Instruments;TI)等SRC的会员公司共享。

最近,SRC又在NRI与STARnet增加了一项结合并扩展研究基准的2年半计划, 目的在于衡量并比较所有研究途径的进展及其优缺点。乔治亚理工学院教授Azad Naeemi负责主持这项衡量基准套件计划。

“我们正着眼于增强和补充互补金属氧化物半导体(CMOS)和场效应电晶体(FET)的所有可用新兴元件,”Naeemi说,“CMOS正接近其微缩限制,因 此全世界都在寻找可用的运算元素,以补强现有的矽晶基础架构。我们的研究将会比较所有可能的选择,包括其优点、限制与瓶颈等。事实上,未来可能不是由单一 种技术主导,而是不同的元件类型可能在不同的应用中运作的更好。”

根据NRI执行总监Tom Theis表示,这项新的基准测试计画真正的好处在于确认哪一种可用的新元件最有希望以及为什么。该基准测试将符合三项设计原则:保持与现有技术的相容性;以新技术类型扩展传统元件;以及扩展直接测量每一种新元件取得优点的方法。

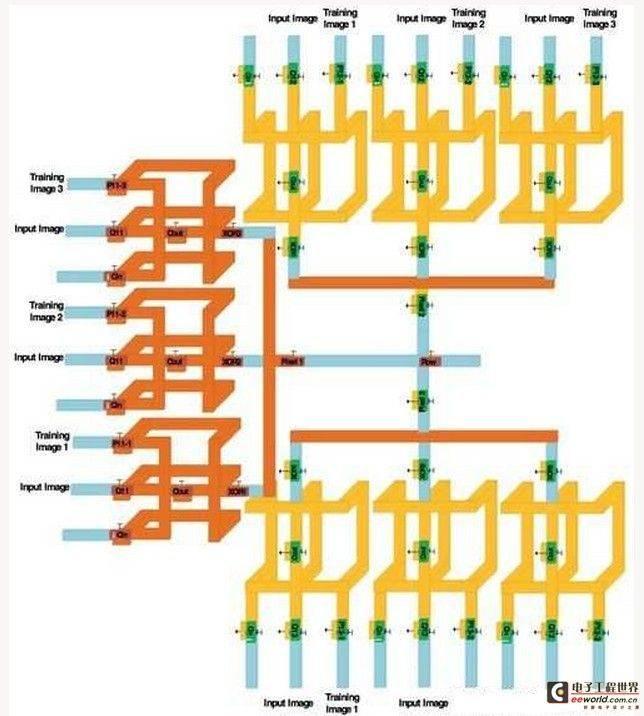

智慧可扩展的全旋检测电路用于辨识低功耗非布林(non-Boolean)模式。图中显示3画素比较器单元(来源:Georgia Tech)

“我们已经有一系列传统的基准了——从NAND和NOR等标准的逻辑功能、加法器和乘法器等标准模组,以及像算术逻辑单元(ALU)等高层次功能,但我们现在 希望扩展该系列,使其涵盖新装置类型所必须提供的功能,”Theis强调,“我们想开发新的基准,它能够延伸至新功能、代表1和0的新方法(如自旋),或 像相变或电荷密度波的多体效应。”

据Theis表示,他们手中有一长串新元件类型的清单,每天都还有新的不断加进来,而且也想帮助其支持者(IBM、Intel、Micron与TI)尽快找到最可能实现成功的是哪一款。他们将为SRC成员公开发布其研究结果,随后也会分享给全球的工程社群。

Naeemi表示,他的研究小组目标在于扩大基准的基础,进一步提升对于元件如何作业以及最适合哪些应用的工程瞭解。

“我们想强调的是,研究人员必须将努力专注于如何利用创新上,因为在这方面力求改善才是最有效率的,这不只对逻辑元件来说是这样,记忆体元件也是如此,”Naeemi说:“极其重要的是把他们都放在一起,就能准确掌握每项研究,对于它们如何进行也瞭若指掌。”

利用穿隧、铁电、磁电与旋矩技术的32位元加法器所表现的能量与延迟

(来源:Intel)

目前一些已经进行基准测试的新元件包括像电晶体般可作业于超低电压下的元件(因而也十分低功耗)、不至于像FET那样结合记忆体与逻辑功能的非挥发磁性元件,以及“运算”像人脑神经网路的非布林类比元件。

该基准测试计划将进行到2017年底。

热门文章

更多

热门文章

更多