引言

在工业现场中,大多的通信设备是通过加装通信模块来实现的,而大多的通信模块的处理器采用ARM核。随着微电子学和计算机科学的迅速发展,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA和嵌入式系统的多种模式。SOPC由于集成了硬核或软核CPU、DSP、存储器、外围I/O及可编程逻辑模块,在设计和应有的灵活性及其成本方面有较大的优势。

NIOSⅡ系列处理器是Altera公司的第二代FPGA嵌入式处理器。同前一代软核的CPU相比,NIOSⅡ的性能得到很大提高,体积更小,其最大处理能力是第一代软核的三倍。逻辑功能方面具有32位的精简指令集CPU。实现方式是在FPGA上通过编程的方式实现,这是与传统的CPU的一个根本的差别。本文是在NIOSⅡ软核的基础上设计了蓝牙技术模块,并在工业以太网中,较好地实现了通信模块与工业现场设备的无线通信。

NIOSⅡ嵌入式处理器概述

NIOSⅡ处理器是Altera公司的第二代用户可配置的通用32位RSIC软核微处理器,是Altera公司特有的基于通用FPGA架构的软 CPU内核。它可以提供:完全的32位指令集、数据总线和地址空间;32位通用的目的寄存器;32个外部中断源;计算64位和128位乘积专用指令;单指令桶形移位器;对多种片上外设进行访问,提供片外存储器和外设接口;在IDE控制下,硬件辅助调试模块可对处理器进行启动、停止、单步和追踪操作;基于 CNU C/C++工具链和Eclipse IDE;所有的NIOSⅡ处理器系统的指令集兼容;具有超过150 DMIPS的性能。

它将设计输入、综合、布局、验证、编程与配置以及第三方EDA工具接口集成在一个无缝的综合性设计环境中。NIOSⅡ的硬件开发环境是在 SOPC builder中进行的。SOPC builder是一个自动化的SOPC硬件系统的开发工具,集成在Quartus Ⅱ软件内,Quartus Ⅱ和SOPC builder一起为建立SOPC设计提供标准化的图形环境。Quartus Ⅱ和SOPC builder软件,可以在很短的时间内定义一个完整的硬件系统。SOPC builder 通过SOPC开发阶段的系统定义、集成和验证的自动化,缩短了产品的市场化时间。

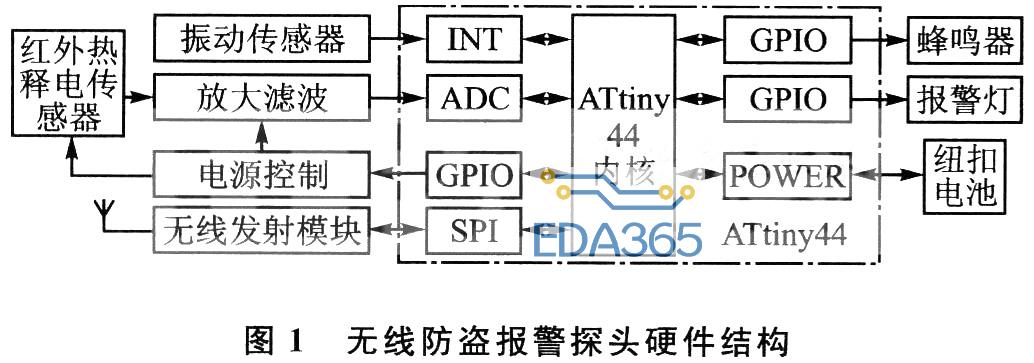

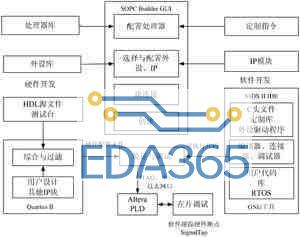

NIOSⅡ软件开发环境被称为NIOSⅡ集成开发环境(Integrated Development Environment,IDE)。它内嵌在Quartus Ⅱ设计工具中,可通过JTAG将应用程序下载到SOPC硬件系统中进行调试,可在指令集仿真器中对应用程序进行仿真调试,也可在ModelSim软件中进行仿真调试。基于NIOSⅡ的SOPC的软硬开发环境及设计流程如图1所示。

图1 基于NIOSⅡ的SOPC软硬件开发环境及流程

首先利用SOPC Builder的界面定制系统,产生输出文件;然后进入传统的FPGA硬件开发流程;在Quartus Ⅱ中进行逻辑综合、布局布线。在软件流程中,用户利用NIOSⅡ IDE环境,建立工程、编译设计、调试等。

蓝牙通信模块的硬件设计

蓝牙技术是一个开放性的、短距离无线通信技术标准,工作在全球通用的2.4GHz ISM频段,采用跳频扩频技术,可以用于近距离通过无线连接的方式实现固定设备以及移动设备之间的网络互连,在各种数字设备之间实现灵活、安全、低成本、小功耗的数据和语音通信,实现全方位的数据传输。

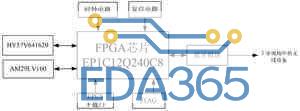

工业现场中存在多种使用不同方法进行互连的设备。对有些环境比较恶劣,布线不方便等因素可以采用蓝牙无线通信技术来实现数据的通信。本设计中,采用了基于NIOSⅡ软核的FPGA芯片EP1C12Q240C8作为CPU处理器,并在处理器的外围拓展了64Mb的SDRAM和16Mb的 Flash,配置了50MHz的时钟、复位电路、下载口,接入蓝牙模块,以便在蓝牙通信模块中实现通信协议并通过蓝牙模块发送测试数据或接收控制命令等。图2为基于NIOSⅡ软核的蓝牙通信模块的硬件设计框图。

图2 基于NIOSⅡ软核的蓝牙通信模块的硬件设计框图

在通信模块上使用了AM29LV160的Flash和HY57V461620的SDRAM。将CPU的存储容量进行了拓展,以便保证在EPA网络上的通信协议的移植和操作系统(Linux、Windows CE)的移植。复位电路是由10kΩ电阻、10μF电容和按键组成的,可实现按键低电平复位和上电低电平复位。

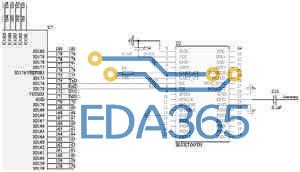

蓝牙模块的实现采用了CSR公司的单芯片BCM04。BCM04内嵌BlueCore04芯片,并提供SPI、UART/USB、PIO、 PCM接口。BCM04中自带8Mb的闪存SST39VF800,工作电压为2.7~3.6V。在天线和发射机输出端之间接入平衡-不平衡转换器。带通滤波器一般是无源器件,它的作用是滤除接收机不需要的频带内的信号,为低噪声放大器(LNA)提供选择性信号起到减小干扰的作用。BCM04中采用了台湾 ACX公司的集成带通滤波器+平衡不平衡转换器的器件FB2520,带通滤波器和平衡-不平衡转换器集成在一起集成度更高有效的减小了电路板的面积,该器件具有外型小巧,插入损耗低等优点,能够很好地完成平衡到不平衡端的转换和带通滤波的功能。BCM04中需要3.3V和 1.5V两种电压,其中1.5V是为蓝牙芯片和带通滤波器+平衡-不平衡转换器供电,3.3V为Flash芯片和蓝牙芯片的外围I/O脚提供电压。CPU 与蓝牙模块接口电路图如图3所示。

图3 CPU与蓝牙接口的电路图

基于NIOSⅡ软核的FPGA芯片的SOPC设计

NIOSⅡ嵌入式处理器是FPGA生产厂商Altera公司推出的软核CPU,是一种面向用户的、可以灵活定制的通用RISC(精简指令集架构)嵌入式CPU。NIOSⅡ以软核方式提供给用户,并专为Altera的FPGA上实现做了优化,用于SOPC集成,最后在FPGA上实现。为完成设计要求,需要对处理器芯片进行配置。其SOPC Builder上的配置如图4所示。

c++相关文章:c++教程

通信相关文章:通信原理

蓝牙技术相关文章:蓝牙技术原理

APP下载

APP下载 登录

登录

热门文章

热门文章