控制模块由单板上的IXP425+CPLD组成。负责单板的资源和信息管理,把从业务单板发送过来的音/视频信号转发给相应的DM642处理。单板CPLD主要实现单板的复位、时钟检测、片选信号控制、寄存器读写、单板信息等功能。音/视频处理模块由单板上4片DM642完成,是单板的核心模块。决定音/视频处理模块性能的有两个关键因素:音/视频算法性能以及PCI总线的传输性能。

为了增强PCI总线的传输性能,可从如下两个方面改善:提高PCI总线传输效率;PCI总线上任何一个器件都可以作为主器件发起传输,这样DSP芯片之间的数据传输不用通过IXP425转发,节约总线带宽。[page]

2.1 IXP425模块

IXP425模块主要包含CPU最小系统、CPLD控制模块、调试模块、网络管理模块等。框图如图2所示。

IXP425自身具有Expansion总线,能使flash、HPI总线设备、SDRAM等设备与内部ASHB挂接,可兼容Intel/Motorola等制式接口,有cs[7:0]8个bank选择,每个块大小为16 MB,若采用WinCE操作系统,Flash空间则至少在20 MB以上,故最小系统设计时利用了cs0及cs1两个bank作为系统存储空间。为了给程序下载模式留下足够的存储空间,又增加了两片16 MB的Flash。Flash连接如图3所示。

由于IXP425内置了专用的SDRAM控制器,根据其接口原则,同时考虑到平台对运算性能留有一定余量,最小系统中对SDRAM部分的设计选用了2片32 MB的SDRAM,硬件兼容128 MB的SDRAM设计。

[page]

2.2 网口设计

IXP425内部有3个与XScale核并行工作的网络处理机NPE,能对外部提供2个MII接口,并行工作的原理使得网络处理性能较好,支持802.3协议内容,标准的MII接口只需外接PHY物理接口芯片,平台中采用了Intel的LXT972A,即能完成与外界数据的交互。当然,变压器的使用也是必须的,利用了HALO生产的TG110-S050N2与RJ45接口挂接,连接示意图如图4所示。由于IXP425内置了MAC控制器,完善的MII接口使得平台的网络应用比较简单而具有针对性。

2.3 音/视频处理模块设计

2.3.1 PCI接口设计

IXP425 PCI控制器外部挂了4片DM642,总线为33MHz,连接示意图如图5所示。IXP425 PCI总线主要完成对DM642的启动加载、芯片配置管理、PCI总线仲裁和媒体流调度。DM642芯片组主要完成音/视频媒体流的编码、音/视频合成的功能。目前的容量为4路音/视频合成,视频算法为H.264,语音算法为AAC、G.723.1等。

其中,DM642A占用IXP425的PCI时隙1,DM642B占用IXP425的PCI时隙2,DM642C占用IXP425的PCI时隙3,DM642D占用IXP425的PCI时隙4,其有差异的对应引脚互连如下:DM642A与IXP425的PCI引脚对应。PCI中断控制信号由CPLD进行会聚后上报给CPU,CPU通过读取CPLD内部的中断寄存器来判断外围PCI设备的中断事件。

2.3.2 音/视频处理模块最小系统设计

EMIFA允许无缝连接多种SDRAM,由于选用的SDRAM大小为64 MB,根据DM642 EMIFA的接口准则,DM642最小系统如图6所示。

芯片选择由CE0完成,选用2片16MB大小的SDRAM进行位扩展后,最大寻址空间为32MB,行地址选通为A[3:10],列地址选通为A[3:14],块选择(bankselect)为A[15:16],故使用DM642地址线A[3:16]。DM642内核工作在50M×12 Hz的模式下,EMIF接口工作在25M x 5.33 Hz,PCI接口工作在33 MHz时钟频率下。

[page]

2.3.3 Flash设计

2.6 JTAG链接

单板CPU、CPLD的JTAG单独成链,方便加载和调试,4片DM642连成一条菊花链,硬件兼容各个芯片单独调试,菊花链框图如图8所示。

3 硬件调试

本多点控制单元的硬件部分主要进行以下调试:

①电源、复位模块调试:焊接电源模块芯片及外围电路,测试+5 V、3.3 V、1.4 V、1.3 V电压输出是否正常。电压输出正常后,焊接复位电路元件,上电后观察复位电压及延续时间是否满足设计要求,用示波器测量复位信号的电平和持续时间等是否与设计相符。上电后注意各电压转换芯片是否烫手,不正常则立即断开电源进行检查。

②最小系统调试:在板上焊接IXP425芯片、DM642芯片、CPLD、SDRAM、Flash、JTAG接口及各模块电路外围元件。用放大器仔细检查有无短路、断路、虚焊、漏焊、假焊等情况。无问题后上电,测量各芯片工作电压是否正常,用示波器和频率计测量各模块的工作时钟是否正常。利用JTAG口将硬件与计算机相连,配置好控制寄存器后,测试SDRAM读写功能是否正常,Flash擦写功能是否正常。如果工作不正常,检查时序信号、硬件连接等情况。

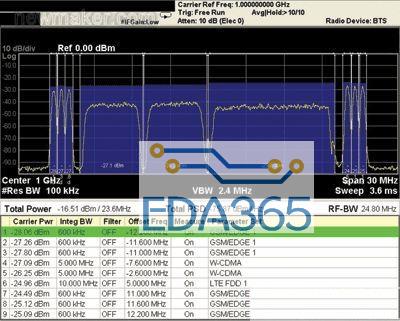

③PCI总线调试:测试各功能模块之间数据传送是否正常,如IXP425读写4块DM642,D642之间读写数据等,需结合计算机、示波器、频谱分析仪、逻辑分析仪等进行测试。

④网络收发模块调试:焊接LTX972A及外围器件。检测IXP425的MII接口与LTX972A芯片之间连接是否正常,通过Intel提供的LTX972A测试程序测试网络收发模块是否能与本地PC机通过网口进行数据通信。

4 结论

本多点控制单元在设计上具有以下特点:

①非PC机的嵌入式会议电视多点控制单元设计;

②内部采用PCI总线连接,解决会议电视多点控制单元内部突发大数据量传输和各数据处理模块的同步问题;

③多并行数据处理模块设计。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多