如果采用双码元间隔升余弦脉冲代表随机二进制序列中的“1”和“0”,且当前脉冲总是在前一个脉冲的中点开始,可以证明由此得到的代表随机二进制序列的波形,其频谱特性和单个双码元间隔升余弦脉冲的特性一样。

分析双码元间隔升余弦脉冲可知,S(t)为一偶函数,且满足如下2个条件:

以上条件保证了由双码元间隔升余弦脉冲同步叠加厚的随机波形为一连续信号,即S(t)和S(t-Ts)之和,在一个码元间隔内任何时刻均为1;而他们之差为一偶函数。由于双码元间隔脉冲在t≥±Ts时,其值为零,因而不存在码间干扰;t=Ts/2时,幅值为峰值的一半,表示数字1和0的正负脉冲同步叠加后,合成波在Ts/2处总为零。因此过零点固定,也不会产生定时抖动。

2.2 IJF非线性滤波器编码方法

实现IJF编码方法有脉冲叠加法,横向滤波器法和非线性滤波器法等几种。非线性滤波器法实质上是一种分段合成IJF波形的方法。

单码元间隔偶脉冲和奇脉冲,根据式(2)可导出:

式(6),(7)表达了无符号间抖动和码间干扰的条件。根据随机二进制数据相邻位(bit)的变化,利用式(3),(4)定义的单间隔脉冲,可导出构成IJF编码的4个基本波形函数S1-S4:

式中xn为当前比特,xn-1为前一比特。

设输入的数据(NRZ)信号为:

他是随输入数据变化的随机序列,其波形可视为4个基本波形的组合,即:

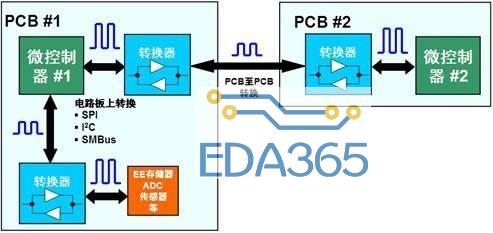

由此可得出非线性转换滤波器IJF编码信号形成的方案,如图1所示。

3 IJF编码的FPGA实现

首先给出一个IJF-OQPSK调制器的组成原理框图如图2所示。其中的串并变换、延时、差分编码和IJF编码采用XILINX公司的FPGA器件SPARTANII XC2S200来实现。I,Q两支路经IJF编码成形的数据通过数/模转换器AD9765转换为模拟幅值送入正交调制器AD6122后得到70MHz中频的IJF-OQPSK调制信号。 [page]

有上述的分析可以看出,IJF-OQPSK调制的关键在于IJF编码。下面重点讨论IJF编码的FPGA实现方法。

由式(9)和图1可看出,IJF编码的过程就是根据前后码元的组合关系去波形系数表中查表,以一定的采样时钟取得相应的波形系数从而实现波形成形。因此首先需要建立波形系数表。假设原始输入数据信息速率为2Mb/s,经过串并转换后I,Q支路码速率为1Mb/s,若以50MHz的时钟采样,则每个码元需要50个波形采样数据,理论上有4种基本波形,需要存储200个波形数据,但S1(t)=+1,S2(t)=-1是固定值,不需要存储单元,只需对进行存储即可,共需要100个存储单元,由于FPGA后端的数/模转换器AD9765为12位,因此存储单元中的地址线宽度为7位,数据线宽度为12位。这里采用XILINX的COREGenerator提供的IP核Single Prot Block Memory来构建ROM用于存储波形系数。此IP核的一些主要特点是:

关于IP核的生成与使用方法可以参考文献[1]。生成的ROM还需向其中添加coe文件,即波形系数表,其文件格式如下:

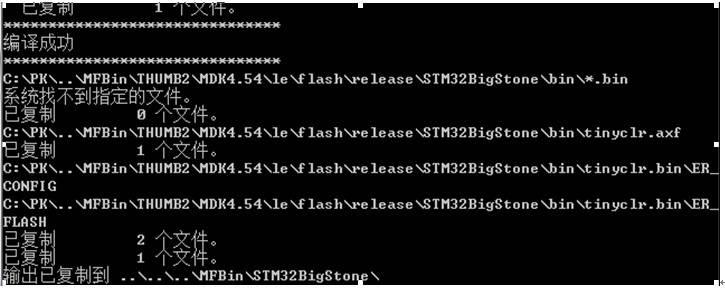

其中关键字MEMORY_INITIALIZATION_RADIX说明了ROM数据的进制(2,10,16可选)。GLOBAL_IN1T_VALUE定义了全局初始值。MEMORY_INITALIZATION_VECTOR即定义了IJE编码的波形系数表。其中前50个系数对应着,后50个系数对应着。最终生成的波形系数ROM如图3所示。此方法生成的ROM将使用FPGA提供的BLOCK RAM,而不会占用distribute RAM,从而节省了宝贵的可编程资源。

4 结语

图4显示了IJF-OQPSP与OQPSK基带编码和调制信号频谱的比较。从图4可以看出,采用时限双码元间隔升余弦脉冲波形进行的IJF编码,在时域具有光滑连续的优点,而且非常适宜于数字实现。已经证明双码元间隔升余弦脉冲波形是时域分布长度有限的最佳波形[2],可以做到理论上的无码间干扰和相位抖动。IJF编码后使得信号的相位路径变得连续、平缓,从而在很大程度上改善了信号的谱性能。由图4可以看到IJF-OQPSK调制信号的功率谱性能明显好于QPSK的功率谱,不仅衰减速度快,而且主瓣宽度与QPSK保持一样的情况下旁瓣宽度压缩为QPSK信号旁瓣宽的一半。通过对其功率谱的分析比较可以看出,IJF-OQPSK调制体制在频谱资源愈显紧张的形势下,具有较大的应用潜力。

本方案采用FPGA和集成器件来实现IJF编码和IJF-OQPSK调制具有高度集成化、配置灵活、性能稳定、易于实现的特点,由于IJF编码有很多性能更好的变形,只需在此基础修改ROM中的波形系数即可进一步实现多种IJF编码方案。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多