近年来,随着个人手持多媒体设备的快速增长,低功耗设计变得越来越重要,甚至成为决定产品是否成功的关键,如笔记本电脑、PDA、移动电话等时尚消费和商务类电子产品,对电池的供电时间要求越来越高,高功耗成为延长电池使用时间突出的制约因素。

CMOS数字电路的功耗主要由3部分组成:跳变功耗、短路功耗和静态漏电功耗。其中占系统功耗比例大于90%的为跳变功耗,也称动态功耗。对于SoC而言,所有的设计方法都是围绕着动态功耗来进行。如何从各个层次、各个方面尽量减少动态功耗,将是语音解码设计中的重点内容。

1 语音解码器的低功耗设计策略

SoC低功耗的设计应该从顶层到底层各个阶段进行优化设计的工作,主要运用各级的低功耗策略,通常在系统级、算法级、结构级、电路级、布局布线以及制造工艺等层次上综合考虑。有研究表明,除了制造工艺外,高抽象层次(系统级、算法级、结构级)的设计因素对功耗的影响比其他层次要大的多。因此系统级、算法级、结构级的低功耗设计技术的研究非常重要。

1.1 系统级的低功耗设计策略

降低系统级的功耗实际上是减少动态功耗。主要方法是时钟采用Power-down管理模式,在SoC处于空闲状态时,使SoC运作于休眠状态(只有部分设备处于工作之中);在预设时间到来时,产生一个中断,由该中断唤醒其他设备;或采用门生时钟技术停掉未工作模块的时钟,从而降低系统功耗。

另外,多时钟设计也是降低系统功耗的有效方法,即让运算量小的模块采用低频率时钟;而运算量大的模块使用高频率时钟。

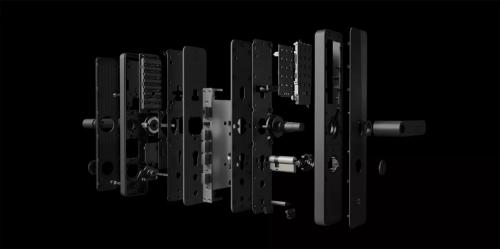

本设计综合使用了上述设计策略以降低系统功耗。使用一个系统主频,通过对时钟的精细控制,即时钟使能&禁止以控制模块的工作状态;使用双向不交叠时钟技术,提高运算量大的模块的操作频率,同时消除了竞争与冒险的可能。双向不交叠时钟由系统时钟Cp分为2个不交叠的时钟,yCp和zCp,如图1所示在运算时,由yCp时钟控制输入数据,由zCD时钟控制取出结果。

1.2 算法级低功耗设计策略

算法级低功耗设计主要在于软件代码的优化,减少由于算法的低效率引起的不必要功耗。一方面是对标准C代码的优化。C语言具有易读性、可移植性,但是C语言在实际工程应用中,不便于对系统硬件资源的直接控制,无法发挥SoC的特点。用汇编语言编程,可以根据芯片自身硬件结构特点,对汇编程序进行优化与精简,往往能够使一些复杂的算法和功能模块在实时处理方面取得非常好的效果。另一方面分析了影响执行效率的数据相关、控制相关和资源冲突等因素后,在手工汇编的基础上充分挖掘算法的潜力,最大限度发挥硬件性能,以达到实时要求和低功耗设计的指标。

在本设计里主要根据SoC平台的资源和指令集特点,使用软硬件协同设计方法在C代码转化为汇编代码时,通过分析标准C算法发现,大部分循环和函数的调用存在冗余,频繁的函数调用操作(压栈出栈)占用了CPU的部分处理时间。在汇编代码中可以通过循环展开以减少不必要的循环判断,其基本原则的原始代码为:普通的单循环,一个周期执行一次乘累加(MAC)指令,优化后进行了4次循环展开。在优化后的代码中,4个MAC被同时使用,并且在作乘累加时,提取下次运算的数据,消除了流水线等待,充分应用了硬件资源,提高了效率。除了循环展开,在某些情况下进行循环合并也可提高效率。主要原因是每个循环体均需要有控制指令,减少循环的个数自然会减少控制指令的条数。注意两个合并的循环必须有相同的循环数。

对于在代码里多次用到的函数,应考虑用调用指令,这样可以大大减少代码的体积;而对于只调用少次的函数,则宜嵌入主函数中,因为它不仅可以减少传参过程中的指令,而且可以减少调用函数的压栈出栈操作。当然,对于一些大而复杂的函数,虽然它只被调用1次,但由于寄存器的数目有限,如果考虑直接嵌入主函数,可能要频繁地做push和pop操作,反而得不偿失,这时就应该用调用指令。

如果有些处理比较复杂,在整个解码过程中运算量大且耗时长,有必要设计相关硬件协处理器,通过汇编指令直接操作协处理器,既可以提高效率减少运算量也有利于控制功耗,但成本会增加。这种处理方法在实时影响明显的模块尤其关键和有效。例如在MP3的解码中,通过增加矩阵乘法器以提高子带综合滤波的处理速度,取得明显效果:可减少运算时间91%。这种软硬件协同的设计手段在语音解码器中多处用到。

在算法级中还涉及其他方面的低功耗设计,如减少存储器的存取次数,缩短片选信号的宽度等方面的考虑,本设计也做了相应的处理。总的说来,算法级的优化设计在降低系统功耗方面潜力大,对降低整个语音解码器的功耗具有重要意义。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多