DRAM模块是大多电子设备均存在的模块之一,大家对于DRAM也较为熟悉。但是,大家真的了解DRAM吗?DRAM的基本单元的结构是什么样的呢?DRAM的工作原理是什么呢?如果你对DRAM具有兴趣,不妨继续往下阅读哦。

一、DRAM介绍

DRAM的英文全称是“DynamicRAM”,翻译成中文就是“动态随机存储器”。DRAM只能将数据保持很短的时间。为了保持数据,DRAM必须隔一段时间刷新(refresh)一次。如果存储单元没有被刷新,数据就会丢失。DRAM用于通常的数据存取。我们常说内存有多大,主要是指DRAM的容量。

所有的DRAM基本单位都是由一个晶体管和一个电容器组成。请看下图:

上图只是DRAM一个基本单位的结构示意图:电容器的状态决定了这个DRAM单位的逻辑状态是1还是0,但是电容的被利用的这个特性也是它的缺点。一个电容器可以存储一定量的电子或者是电荷。一个充电的电容器在数字电子中被认为是逻辑上的1,而“空”的电容器则是0。电容器不能持久的保持储存的电荷,所以内存需要不断定时刷新,才能保持暂存的数据。电容器可以由电流来充电——当然这个电流是有一定限制的,否则会把电容击穿。同时电容的充放电需要一定的时间,虽然对于内存基本单位中的电容这个时间很短,只有大约0.2-0.18微秒,但是这个期间内存是不能执行存取操作的。

DRAM制造商的一些资料中显示,内存至少要每64ms刷新一次,这也就意味着内存有1%的时间要用来刷新。内存的自动刷新对于内存厂商来说不是一个难题,而关键在于当对内存单元进行读取操作时保持内存的内容不变——所以DRAM单元每次读取操作之后都要进行刷新:执行一次回写操作,因为读取操作也会破坏内存中的电荷,也就是说对于内存中存储的数据是具有破坏性的。所以内存不但要每64ms刷新一次,每次读操作之后也要刷新一次。这样就增加了存取操作的周期,当然潜伏期也就越长。SRAM,静态(StaTIc)RAM不存在刷新的问题,一个SRAM基本单元包括4个晶体管和2个电阻。它不是通过利用电容充放电的特性来存储数据,而是利用设置晶体管的状态来决定逻辑状态——同CPU中的逻辑状态一样。读取操作对于SRAM不是破坏性的,所以SRAM不存在刷新的问题。

SRAM不但可以运行在比DRAM高的时钟频率上,而且潜伏期比DRAM短的多。SRAM仅仅需要2到3个时钟周期就能从CPU缓存调入需要的数据,而DRAM却需要3到9个时钟周期(这里我们忽略了信号在CPU、芯片组和内存控制电路之间传输的时间)。

二、基本原理

DRAM由晶体管和小容f电容存储单元组成。每个存储单元都有一小的蚀刻晶体管,这个晶体管通过小电容的电荷保持存储状态,即开和关。电容类似于小充电电池。它可以用电压充电以代表1,放电后代表0,但是被充电的电容会因放电而丢掉电荷,所以它们必须由一新电荷持续地“刷新气。

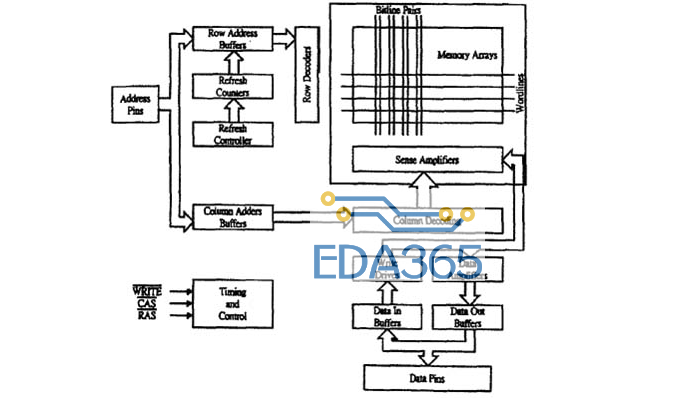

下图所示的是标准的DRAM结构的框架图,和SRAM不同的是,标准DRAM的地址线分成两组以减少输入地址引脚的数量,提高封装的效率。虽然在标准的DRAM结构中,输入地址引脚的数量可以通过安排多元的地址方式来减少,但是这样的话,标准DRAM存储单元的时钟控制就会变得更加复杂,同时运行速度会受到影响。为了满足对于高速DRAM应用的需求,一般都用分开的地址输入引脚来减少时钟控制的复杂性和提高运行速度。

DRAM的控制器提供行地址选通脉冲-M(RowAddressStrobe)和列地址选通脉冲CAS(ColumnAddressStrobe)来锁定行地址和列地址。正如图所示,标准DRAM的引脚为:

地址:分成两组,行地址引脚,列地址引脚;

地址控制信号引脚:RAS和CAS;

写允许信号:WRITE;

数据输入/输出引脚;

电源引脚。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多