虽然很多人对DRAM不太熟悉,但是DRAM却并非新奇玩意儿。因为,在使用电脑的时候,我们都在和DRAM打交道。为增进大家对DRAM的认识程度,本文将基于两点对DRAM予以介绍:1.DRAM的组织方式介绍,2.DRAM模块介绍。如果你对DRAM及其相关知识具有兴趣,不妨继续往下阅读哦。

一、DRAM组织方式介绍

随着系统对内存容量、带宽、性能等方面的需求提高,系统会接入多个DRAMDevices。而多个DRAMDevices不同的组织方式,会带来不同的效果。本文将对不同的组织方式及其效果进行简单介绍。

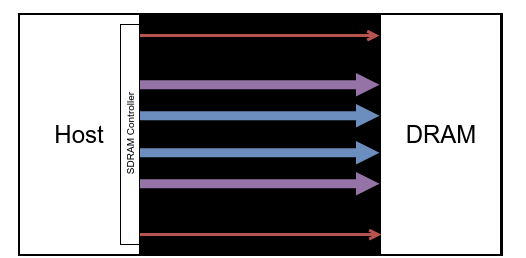

1.SingleChannelDRAMController组织方式

SingleChannel指DRAMController只有一组控制和数据总线。在这种场景下,DRAMController与单个或者多个DRAMDevices的连接方式如下所示:

1.1连接单个DRAMDevice

SingleChannel连接单个DRAMDevice是最常见的一种组织方式。由于成本、工艺等方面的因素,单个DRAMDevice在总线宽度、容量上有所限制,在需要大带宽、大容量的产品中,通常接入多个DRAMDevices。

1.2连接多个DRAMDevices

上图中,多个DRAMDevices共享控制和数据总线,DRAMController通过ChipSelect分时单独访问各个DRAMDevices。此外,在其中一个Device进入刷新周期时,DRAMController可以按照一定的调度算法,优先执行其他Device上的访问请求,提高系统整体内存访问性能。

NOTE:CS0和CS1在同一时刻,只有一个可以处于使能状态,即同一时刻,只有一个Device可以被访问。

上述的这种组织方式只增加总体容量,不增加带宽。下图中描述的组织方式则可以既增加总体容量,也增加带宽。

上图中,多个DRAMDevices共享控制总线和ChipSelect信号,DRAMController同时访问每个DRAMDevices,各个Devices的数据合并到一起,例如Device1的数据输出到数据总线的DATA[0:7]信号上,Device2的数据输出到数据总线的DATA[8:15]上。这样的组织方式下,访问16bits的数据就只需要一个访问周期就可以完成,而不需要分解为两个8bits的访问周期。

2.MulTIChannelDRAMController组织方式

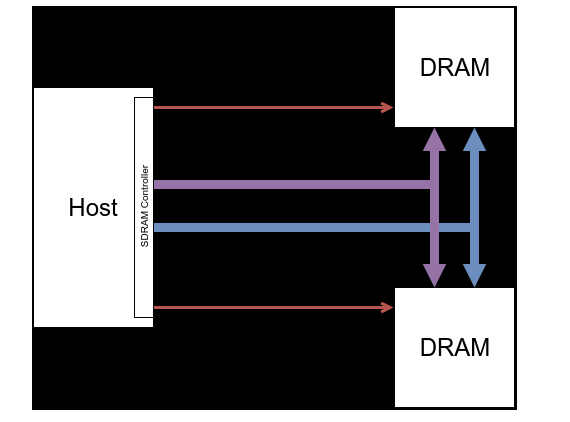

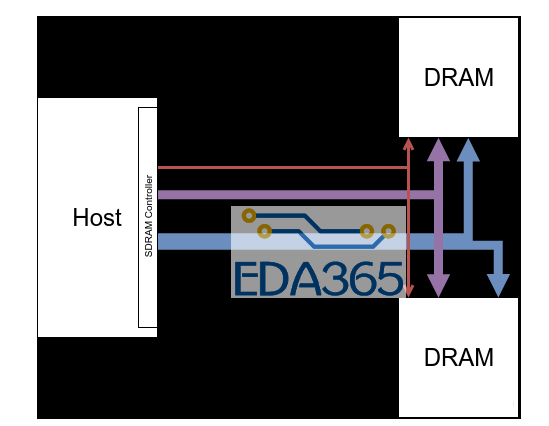

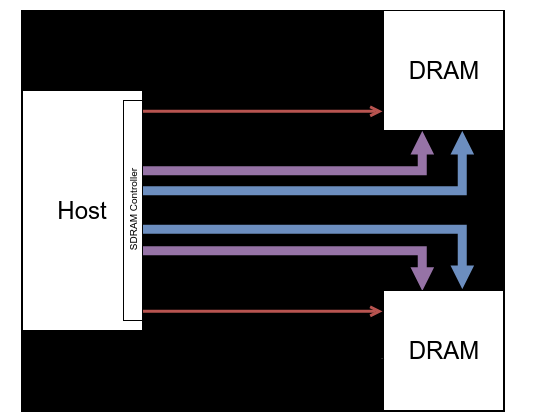

MulTIChannel指DRAMController只有多组控制和数据总线,每一组总线可以独立访问DRAMDevices。在这种场景下,DRAMController与DRAMDevices的连接方式如下所示:

2.1连接SingleChannelDRAMDevices

这种组织方式的优势在于多个Devices可以同时工作,DRAMController可以对不同Channel上的Devices同时发起读写请求,提高了读写请求的吞吐率。

NOTE:CS0和CS1在同一时刻,可以同时处于使能状态,即同一时刻,两个Devices可以同时被访问。

2.2连接MulTIChannelDRAMDevice

在一些DRAM产品中,例如LPDDR3、LPDDR4等,引入了MulTIChannel的设计,即一个DRAMDevices中包括多个Channel。这样就可以在单个Device上达成MultiChannel同时访问的效果,最终带来读写请求吞吐率的提升。

二、DRAM模块

DRAM的英文全称是“DynamicRAM”,翻译成中文就是“动态随机存储器”。。DRAM只能将数据保持很短的时间。为了保持数据,DRAM必须隔一段时间刷新(refresh)一次。如果存储单元没有被刷新,数据就会丢失。DRAM用于通常的数据存取。我们常说内存有多大,主要是指DRAM的容量。

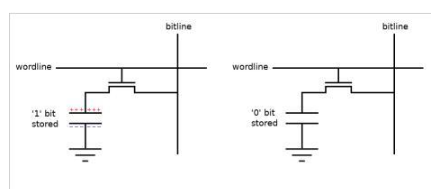

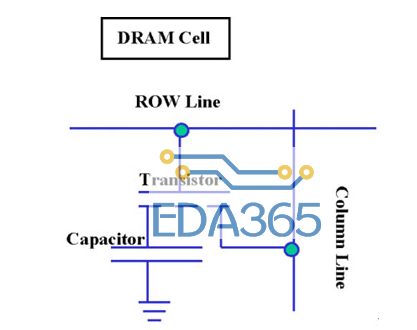

所有的DRAM基本单位都是由一个晶体管和一个电容器组成。请看下图:

上图只是DRAM一个基本单位的结构示意图:电容器的状态决定了这个DRAM单位的逻辑状态是1还是0,但是电容的被利用的这个特性也是它的缺点。一个电容器可以存储一定量的电子或者是电荷。一个充电的电容器在数字电子中被认为是逻辑上的1,而“空”的电容器则是0。电容器不能持久的保持储存的电荷,所以内存需要不断定时刷新,才能保持暂存的数据。电容器可以由电流来充电——当然这个电流是有一定限制的,否则会把电容击穿。同时电容的充放电需要一定的时间,虽然对于内存基本单位中的电容这个时间很短,只有大约0.2-0.18微秒,但是这个期间内存是不能执行存取操作的。

DRAM制造商的一些资料中显示,内存至少要每64ms刷新一次,这也就意味着内存有1%的时间要用来刷新。内存的自动刷新对于内存厂商来说不是一个难题,而关键在于当对内存单元进行读取操作时保持内存的内容不变——所以DRAM单元每次读取操作之后都要进行刷新:执行一次回写操作,因为读取操作也会破坏内存中的电荷,也就是说对于内存中存储的数据是具有破坏性的。所以内存不但要每64ms刷新一次,每次读操作之后也要刷新一次。这样就增加了存取操作的周期,当然潜伏期也就越长。SRAM,静态(Static)RAM不存在刷新的问题,一个SRAM基本单元包括4个晶体管和2个电阻。它不是通过利用电容充放电的特性来存储数据,而是利用设置晶体管的状态来决定逻辑状态——同CPU中的逻辑状态一样。读取操作对于SRAM不是破坏性的,所以SRAM不存在刷新的问题。

SRAM不但可以运行在比DRAM高的时钟频率上,而且潜伏期比DRAM短的多。SRAM仅仅需要2到3个时钟周期就能从CPU缓存调入需要的数据,而DRAM却需要3到9个时钟周期(这里我们忽略了信号在CPU、芯片组和内存控制电路之间传输的时间)。

责任编辑人:CC

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多