NAND闪存诞生这么多年,它的发展一直没有停下来,基本上都是追求跟高的存储密度,所以从最初的SLC一直发展到现在的QLC,虽然存储密度大幅度提升,但论性能的话还最初的SLC更快。在2020年闪存峰会上,NEO半导体首席执行官兼创始人Andy Hsu介绍了他们公司的新X-NAND闪存架构,新的架构有望把SLC的速度与QLC的高密度与低价结合在一起。

消息来自tomshardware,该公司称X-NAND的随机读写与写入比QLC闪存快三倍,连续读取快27倍,连续写入快14倍,从性能来看确实非常之快。

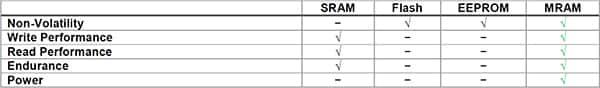

此外芯片的尺寸更小,Die Size只有同样16 planes的NAND闪存的37%,这样就可以有更好的灵活性,可以根据实际需要缩减芯片的尺寸,而且X-NAND在较小的尺寸下依然有较高的并行性,就像智能手机或者M.2 SSD上看到的那样,可以在不影响耐用性和成本的情况下实现这一目标,而且它的功耗非常低。

现在的QLC SSD严重依赖SLC Cache,因为QLC的原始写入速度实在太低了,所以QLC SSD基本上都会利用它的容量优势配备大容量SLC Cache,在消费级市场上通常来说写入压力不会很大,所以有足够的空闲时间把SLC缓冲区搬运到QLC闪存上存储,但企业级负载就没有这样的时间了。X-NAND允许同时进行SLC和QLC写入模式,这样就能让闪存一直保持SLC的性能。

西数预计到2024年闪存市场上QLC的份额可能高达50%,X-NAND的设计目标是确保使用现有NAND的方案,传统的NAND工艺无需进行结构更改,没有额外的制造成本,并且可以通过快速采样开发,该设计旨在加快QLC的推广应用,特别是在数据中心市场,让QLC的性能不再是瓶颈。

同时X-NAND对编程与擦除策略进行了修改,这样可以提高QLC闪存的耐用性,X-NAND把页面缓冲区从16KB改到1KB,不过Plane的大小可以做到16倍。

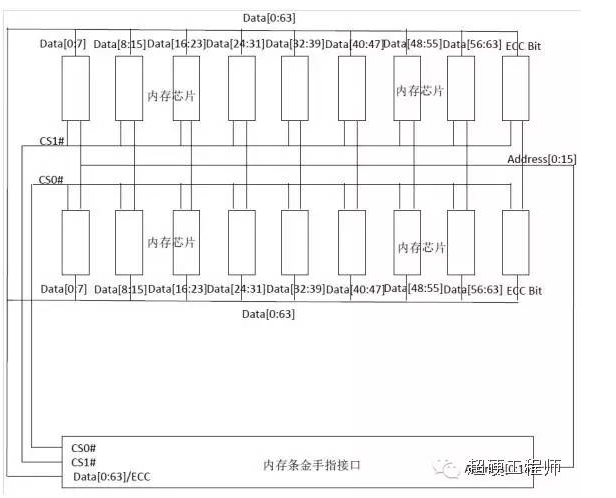

Plane是闪存的最小单位,每个Die里面有一个或者多个Plane,页面缓冲区保存总线与闪存之间保存的数据。闪存芯片被划分为保护位线或单元串的Plane,因此Plane划分可以减少位线的长度,从而有助于提高性能。通过在相邻位线之间进行屏蔽以减少读取或验证编程时的建立时间,可以进一步增强此技术。由于可以并行编程多达十六个位线,因此提高了写入性能。

X-NAND具有六个主要功能:多位线写入,多Plane QLC编程,编程挂起,多BL读取,单锁存QLC读取以及SLC/QLC并行编程。取决于实现方式,由于可以在编程序列中使用多个Plane,因此可以大大提高程序的吞吐量。

使用多个存储体可以同时进行SLC和QLC编程,从而确保SLC页面永远不会满载,同时可以以SLC速度将数据转存到QLC页面。程序允许使用内部共享的页间缓冲区数据线或I/O总线来最大程度地减少额外的延迟。通过使用Plane锁存每个位线的读取来改进读取,并且可以像DRAM一样用非破坏性的方式来刷新数据。

X-NAND可以与任何数量的现有NAND配合使用,从而提高了灵活性并简化了转换。NEO半导体希望该技术具有成本效益,快速且易于在现有设计中实施,该公司表示,它对于像QLC这样的高密度闪存特别有用,因为它可以利用高容量,兼顾高性能和较小的芯片面积,同时又有良好的耐久性和功耗,该技术针对嵌入式设备、AI和云,包括NAS、数据中心和边缘计算。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多