先提一下位宽的概念,对于具体器件而言,它的位宽是一定的,所谓位宽,指的是“读/写操作时,最小的数据单元”──别说最小单元是“位”,一般设备上没有单独的“位操作”,修改位时通过把整个字节、字或双字读出来、修改,再回写。AM29L800BB这种nor flash位宽是16位。K4S561632C这种SDRAM位宽是32位。

对于CPU来说,一个地址对应的是一个字节(8位),也就是说CPU的地址线(A0~A20)对应的最小数据单元是字节。

这里需要注意的是,不要把“外设的位宽”和“CPU的位数”这两个概念混淆了。外设的位宽是读写外设的最小数据单元,CPU位数是CPU可以一次处理的字节数,32位CPU可以一次处理4字节数据。

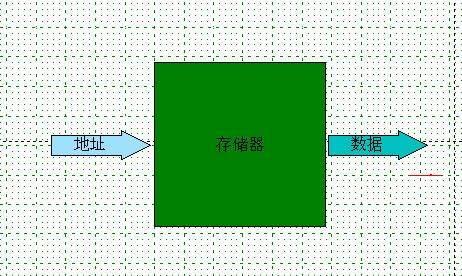

好了,相信你也已经发现问题了吧。既然CPU最小数据单元是8位,flash位宽是16位,那在我们写程序时会特意进行16位操作吗?显然不会,我们写代码时,可不管外设到底是多少位。这是如何实现的呢?原因在于存储控制器(Memory Controller)这个中间层。

存储控制器根据NOR FLASH的位宽,每次总是读/写16位数据。

以读操作为例:

CPU进行8位操作时,它选择其中的8位返回给CPU;

CPU进行16位操作时,它直接把这16位数据返回给CPU;

CPU进行32位操作时,它发起2次读/写,把结果组合成32位返回给CPU。

现在的连线是:CPU的(ADDR1-ADDR20)接到 16位的NOR FLASH (A0-A19),即CPU的ADDR0不接──这说明:不管ADDR0是0还是1,NOR FLASH接收到的地址是一样的。

CPU发出地址0bxxxxxxxxx0、0bxxxxxxxxx1时,NOR FLASH看到的都是0bxxxxxxxxx,返回给存储控制器的都是同一个16位数据。再由Memory Controller选择其中的低8位或高8位给CPU。

存储控制器会做以下事情:

软件要读取地址0上的8位数据时,硬件是这样进行的:

① Memory Controller发出0b000000000000000000000的地址信号,NOR FLASH的A0-A19线上的信号是:0b00000000000000000000

② NOR FLASH在数据总线D0~D15上提供一个16位的“最小数据单元”的数据;

③ 存储控制器读入16位数据;

④ 存储控制器把16位数据的低8位返回给CPU,就得到了一个8位数据。

软件要读取地址1上的8位数据时,硬件是这样进行的:

① 存储控制器发出0b000000000000000000001的地址信号,NOR FLASH的A0-A19线上的信号是:

0b00000000000000000000

② NOR FLASH在数据总线D0~D15上提供一个16位的数据,这是NOR FLASH中的第1个“最小数据单元”

③ 存储控制器读入这个16位数据

④ 存储控制器把这个16位数据的高8位(注意,前面的低8位)返回给CPU,这就是一个8位数据。

所以:

外设位宽是8时,CPU的A0~AXX与外设的A0~AXX直接相连

外设位宽是16时,CPU的A1~AXX与外设的A0~AYY直接相连,表示不管CPU的A0是0还是1,外设看到的都是同一个地址,

对应16位的数据,存储控制器对数据进行选择或组合,再提供给CPU。

外设位宽是32时,CPU的A2~AXX与外设的A0~AZZ直接相连,表示不管CPU的A0A1是00,01,10还是11,外设看到的都是

同一个地址,对应32位的数据,“Memory Controller”对数据进行选择或组合,再提供给CPU。

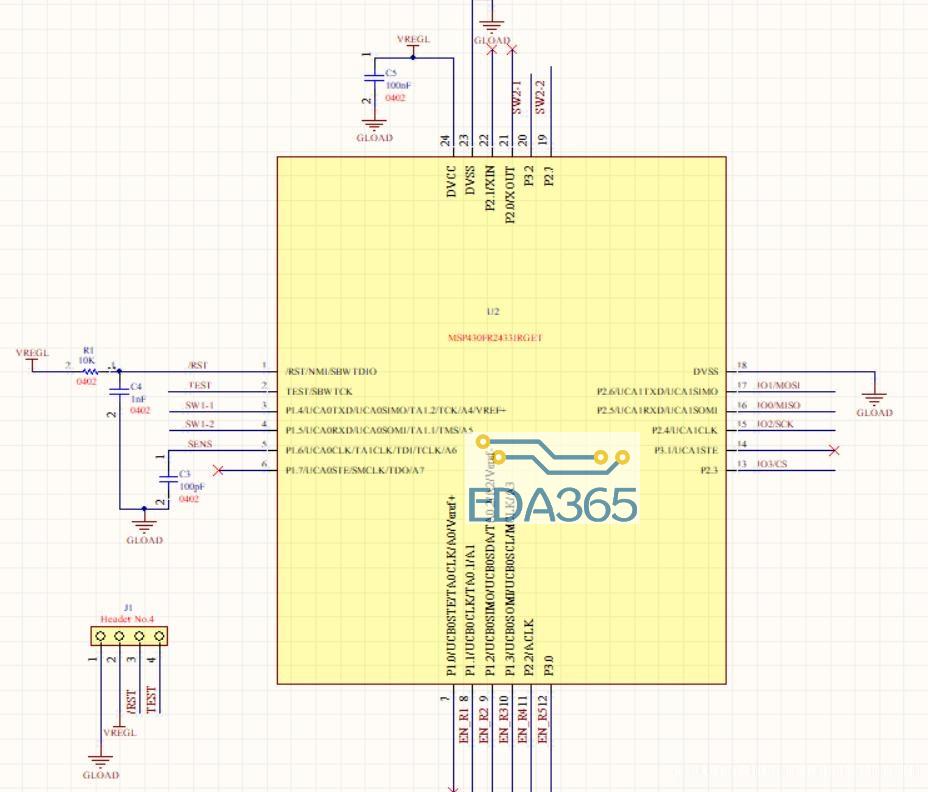

经过以上分析,我们应该知道了,为什么地址线要偏移几位了。同样的SDRAM因为是32位宽的,所以偏移2位。那为什么SDRAM要连ADDR2~ADDR14和ADDR24、ADDR25呢?同样,我们先看下SDRAM的基本知识。

SDRAM的连接方式与上面FLASH的类似,但是要比其复杂些。因为SDRAM内部是一个存储阵列,如同表格一样将数据填进去,因此得先指定一个行,再指定一个列,才可以找到所需的单元格。这个表格被称为逻辑Bank(L-Bank),一般有4个Bank。可以想象,对SDRAM的访问分为以下4个步骤:

① CPU发出片选信号nSCS0有效,选中SDRAM芯片;

② 选择L-Bank,最开始说的ADDR24和ADDR25即此作用;

③ 进行统一行/列寻址;

根据SDRAM芯片的列地址线数目设置CPU相关存储器后,CPU就会从32位的地址中自动分出L-Bank选择信号、行地址信号、列地址信号,然后先发出行地址信号、列地址信号。L-Bank选择信号在发出行地址信号的同时发出,并维持到列地址信号结束。在本例中,行地址、列地址公用ADDR2~ADDR14。K4S561632行地址13,列地址9,所以nSRAS信号有效时,ADDR2~ADDR14发出行地址,对应32位地址空间的bit[23:11];nSCAS有效时,ADDR2~ADDR10发出列地址,对应32位地址空间的bit[10:2]。而bank选择位对应bit[25:24]。这样就构成了64M地址空间,及30000000到33ffffff。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多