LPC1788和LPC1768的外部晶振都是12M,但是LPC1788可以达到120M,而LPC1768的主频只能达到100M。查资料发现这个和PLL0配置的有关系。锁相环(PLL)的作用是把一个输入频率“放大”后输出,输出的频率在通过CCLKSEL 配置后变成CPU时钟频率。观察LPC1788和LPC1768的主频配置时发现两者的PLL0配置相差挺多的。

1788配置:

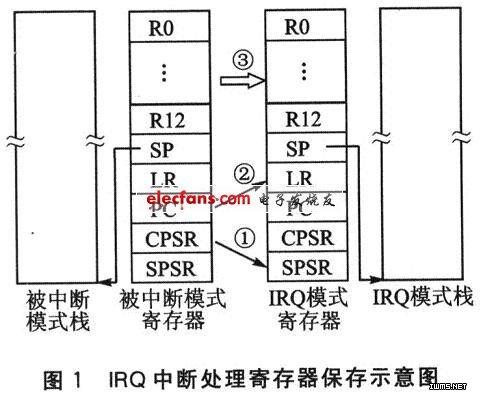

1788的PLL原理图:

其中MSEL和PSEL分别是指PLL倍频器值(M)和PLL分频器值(P)。在LPC1788的寄存器PLL0CFG可以设置。Fcco指PLL振荡器的频率。

所以根据上图 PLL的输出频率 PLL_out_clk =PLL_in_clk x M 或PLL_out_clk = Fcco/(2xP)

可以看出PLL输出频率只由PLL_in_clk和M值决定,而P值是用来决定Fcco的(Fcco限制工作范围是156MHz~320MHz)

Keil中LPC1788的时钟配置:

外部晶振为12MHz,可以算出PLL_out_clk = 12MHz x 10 = 120MHz

而LPC1788的主频率 cclk = PLL_out_clk / CCLKDIV = 120MHz / 1 = 120MHz

LPC1788外设时钟的配置:

外设时钟的配置就是在主频后再分频得到的,通过配置CPU 时钟选择寄存器。

LPC1788配置出来的外设时钟都是统一的值。

Keil中外设时钟显示值:

图中的PCLK就是各个外设相同的时钟。

LPC1768时钟配置:

LPC1768的PLL原理图

LPC1788的PLL工作方式不同,LPC1768的PLL是先分频和倍频,Fcco就等于输出的PLL频率。于是 PLL_out_clk = Fcco = PLL_in_clk x M x 2 / N,可以看出PLL输出频率与M值和N值都有关。

Keil中LPC1768时钟配置

外部晶振同样是12MHz, 于是PLL_out_clk = Fcco = 12MHz x100 x 2 / 6 = 400MHz

而LPC1768的主频 CCLK= PLL_out_clk / CCLKSEL = 400MHz / 4 =100MHz

对于LPC1768外设时钟可以通过Keil中的界面进行设置:

其原理就是通过配置寄存器PCLKSEL0和PCLKSEL1来达到分频的效果。

具体分频配置如下:

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多