1.时钟:用低频晶体和含有倍频器的振荡器可以满足时钟系统速度与低功耗这两个要求。

2.基础时钟模块有三个时钟输入源:

LTXTICLK,低频时钟源(32768HZ)

XT2CLK,高频时钟源

DCOCLK,数字控制RC振荡器

这些模块可提供三种时钟信号:

ACLK辅助系统时钟:由LFXTICLK经分频得到的。一般用于低速外设,可以用软件选择各个外围模块的时钟信号。

MCLK系统主时钟:主要用于CPU和系统。可由上述三种任意来源提供。

SMCLK子系统时钟:可选择LTXICLK+DCOCLK,或者XT2CLK+DCOCLK,主要用于高速外围模块。

3.低频晶体振荡器默认工作在低频模式,即32768HZ。也可以外接高频晶体450kHZ-8MHZ。

高频晶体振荡器的限定了外接450kHZ-8MHZ的晶振。

DCO振荡器:当振荡器失效时,DCO自动被选作MCLK的时钟源。

BCSCTL2:

SELM.0,SELM.1:选择MCLK时钟源。0为DCOCLK(默认)。1为DCOCLK. 2为XT2CLK. 3为LFXTICLK.

DIVM.0,DIVM.1:选择MCLK分频(1,2,4,8)。

SELS:选择SMCLK时钟源。 0(DCOCLK),1(XT2CLK).

DIVS.0,DIVS.1:选择SMCLK分频(1,2,4,8).

DCOR:选择DCO电阻,0为内部电阻,1为外部电阻。

BCSCTL1:

XT2OFF:XT2振荡器的开启和关闭。0为开启,1为关闭。默认关闭。

XTS:控制LFXT1的工作模式,0为低频模式,1为高频模式,这需要结合实际晶体连接情况。

DIVA0,DIVA1,:控制ACLK分频。ACLK只来自于LFXT1所以不用选择只控制分频即可用。

XT5V:0.

RSEL.0,RESL.1,RESL.2(0-7)控制内部电阻以决定标称DCO频率。

RSEL是用来选择电阻的大小,从而控制流过DCO的电流,从而控制频率。

DCOCTL:

DCO0-DCO2跟RSEL共同控制DCO的频率。DCO的每一STEP增加了10%。

4.IE1,IFG1

寄存器IE1中的OFIE如果为1表示:允许晶振错误中断。

寄存器IFG1中的OFIFG如果是0表示外部晶振均起震。

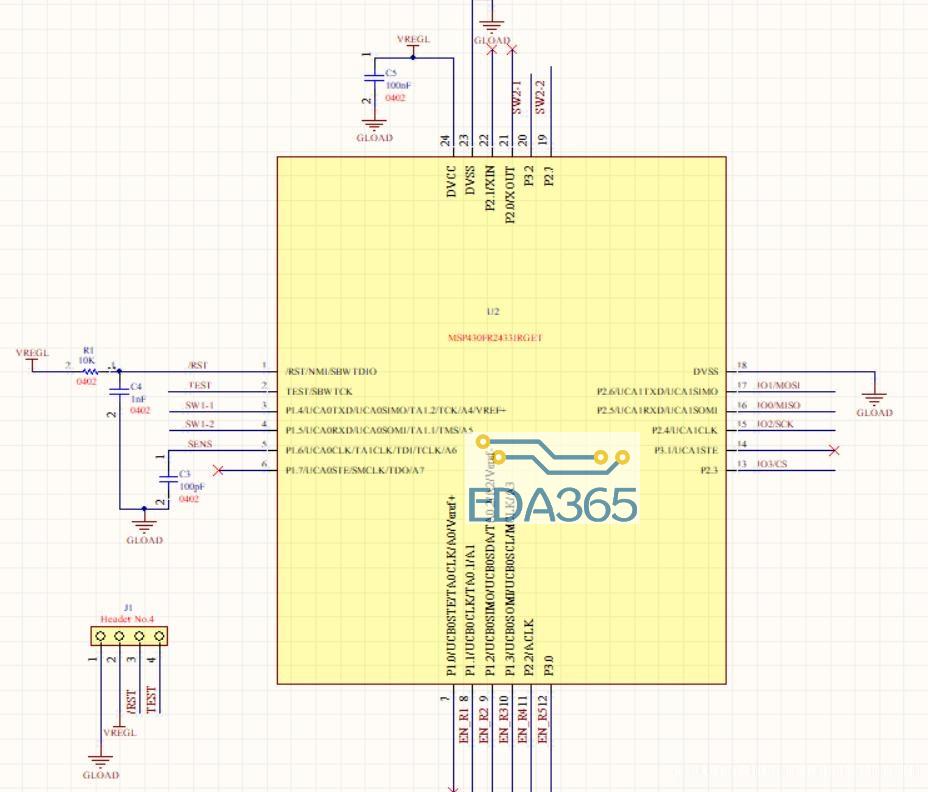

5.默认MCLK是主系统时钟。切换流程如下:

WDTCTL = WDTPW+WDTHOLD;

P5DIR |= BIT4;

P5SEL |= BIT4;//P5.4输出MCLK

BCSCTL1 &= ~XT2OFF;//使用外部高频晶振

do{

IFG1 &= ~OFIFG;

for (i=0XFF;i>0;i--);

}while((IFG1 & OFIFG)); //清除OFIFG FLAG,测试OFIFG是否真的被清除,即外部晶振是否起震。

BSCTL2 |= SELM_2;

for(;;);

}

关键字:MSP430 时钟模块『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多