1. 以太网简介

STM32F42x 系列控制器内部集成了一个以太网外设,它实际是一个通过DMA 控制器进行介质访问控制(MAC),它的功能就是实现MAC 层的任务。

借助以太网外设,STM32F42x 控制器可以通过ETH 外设按照IEEE 802.3-2002 标准发送和接收MAC 数据包。

ETH 内部自带专用的DMA 控制器用于MAC,ETH 支持两个工业标准接口介质独立接口(MII)和简化介质独立接口(RMII)用于与外部PHY 芯片连接。MII 和RMII 接口用于MAC数据包传输,ETH 还集成了站管理接口(SMI)接口专门用于与外部PHY 通信,用于访问PHY 芯片寄存器。

物理层定义了以太网使用的传输介质、传输速度、数据编码方式和冲突检测机制,PHY 芯片是物理层功能实现的实体,生活中常用水晶头网线+水晶头插座+PHY 组合构成了物理层。

ETH 有专用的DMA 控制器,它通过AHB 主从接口与内核和存储器相连,AHB 主接口用于控制数据传输,而AHB 从接口用于访问“控制与状态寄存器”(CSR)空间。在进行数据发送是,先将数据有存储器以DMA 传输到发送TX FIFO 进行缓冲,然后由MAC 内核发送;接收数据时,RX FIFO 先接收以太网数据帧,再由DMA 传输至存储器。

2. SMI 接口 (站管理接口)

SMI是MAC内核访问PHY寄存器标志接口,它由两根线组成,数据线MDIO和时钟线MDC。SMI支持访问32个PHY,这在设备需要多个网口时非常有用,不过一般设备都只使用一个PHY。PHY芯片内部一般都有32个16位的寄存器,用于配置PHY芯片属性、工作环境、状态指示等等,当然很多PHY芯片并没有使用到所有寄存器位。MAC内核就是通过SMI向PHY的寄存器写入数据或从PHY寄存器读取PHY状态,一次只能对一个PHY的其中一个寄存器进行访问。SMI最大通信频率为2.5MHz,通过控制以太网MAC MII地址寄存器 (ETH_MACMIIAR)的CR位可选择时钟频率。

2.1 SMI帧格式

一般由PHY硬件设计决定,所以是固定不变的。

2.2 SMI 读写操作

3. MII 和 RMII接口

MII : Media-independent interface,即介质独立接口,介质独立接口 (MII) 定义了 10 Mbit/s 和 100 Mbit/s 的数据传输速率下 MAC 子层与 PHY 之 间的互连。

RMII: Reduced media-independent interface, 即精简介质独立接口。

TX_CLK:数据发送时钟线。标称速率为10Mbit/s时为2.5MHz;速率为100Mbit/s时为25MHz。RMII接口没有该线

RX_CLK:数据接收时钟线。标称速率为10Mbit/s时为2.5MHz;速率为100Mbit/s时为25MHz。RMII接口没有该线。

TX_EN:数据发送使能。在整个数据发送过程保存有效电平。

TXD[3:0]或TXD[1:0]:数据发送数据线。对于MII有4位,RMII只有2位。只有在TX_EN处于有效电平数据线才有效。

CRS:载波侦听信号,由PHY芯片负责驱动,当发送或接收介质处于非空闲状态时使能该信号。在全双工模式该信号线无效。

COL:冲突检测信号,由PHY芯片负责驱动,检测到介质上存在冲突后该线被使能,并且保持至冲突解除。在全双工模式该信号线无效。

RXD[3:0]或RXD[1:0]:数据接收数据线,由PHY芯片负责驱动。对于MII有4位,RMII只有2位。在MII模式,当RX_DV禁止、RX_ER使能时,特定的RXD[3:0]值用于传输来自PHY的特定信息。

RX_DV:接收数据有效信号,功能类似TX_EN,只不过用于数据接收,由PHY芯片负责驱动。对于RMII接口,是把CRS和RX_DV整合成CRS_DV信号线,当介质处于不同状态时会自切换该信号状态。

RX_ER:接收错误信号线,由PHY驱动,向MAC控制器报告在帧某处检测到错误。

REF_CLK:仅用于RMII接口,由外部时钟源提供50MHz参考时钟。

因要达到100Mbit/s传输速度,MII和RMII数据线数量不同,使用MII和RMII在时钟线的设计是完全不同的。

对于MII接口,一般是外部为PHY提供25MHz时钟源,再由PHY提供TX_CLK和RX_CLK时钟。

对于RMII接口,一般需要外部直接提供50MHz时钟源,同时接入MAC和PHY。

4. MAC 802.3

适用于局域网 (LAN) 的 IEEE 802.3 国际标准将 CSMA/CD(带有冲突检测的载波侦听多路 访问)用作访问方法。

以太网外设包括一个带介质独立接口 (MII) 的 MAC 802.3(介质访问控制)控制器和一个专 用 DMA 控制器。

MAC 模块对以下系列的系统使用 LAN CSMA/CD 子层:数据速率为 10 Mbit/s 和 100 Mbit/s 的基带系统和宽带系统。支持半双工和全双工工作模式。冲突检测访问方法仅适用于半双工工作模式。支持 MAC 控制帧子层。

4.1 MAC 802.3 帧格式

正如 IEEE 802.3-2002 标准规定,MAC 块使用 MAC 子层和可选 MAC 控制子层 (10/100 Mbit/s)。

为使用 CSMA/CD MAC 的数据通信系统指定了两个帧格式:

● 基本 MAC 帧格式

● 标记 MAC 帧格式(扩展了基本 MAC 帧格式)

通过以下条件之一定义无效 MAC 帧:

● 帧长度与长度 / 类型字段指定的预期值不一致。如果长度 / 类型字段包含类型值,则认为

帧长度与此字段一致(没有无效帧)

● 帧长度不是字节的整数倍(额外位)

● 根据传入帧计算出的 CRC 值与包含的 FCS 不匹配

4.2 MAC数据包发送和接收

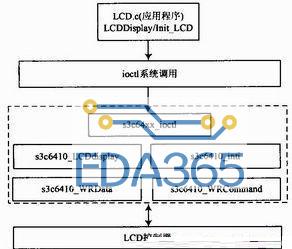

ETH外设负责MAC数据包发送和接收。利用DMA从系统寄存器得到数据包数据内容,ETH外设自动填充完成MAC数据包封装,然后通过PHY发送出去。在检测到有MAC数据包需要接收时,ETH外设控制数据接收,并解封MAC数据包得到解封后数据通过DMA传输到系统寄存器内。

4.2.1 MAC数据包发送

MAC数据帧发送全部由DMA控制,从系统存储器读取的以太网帧由DMA推入FIFO,然后将帧弹出并传输到MAC内核。帧传输结束后,从MAC内核获取发送状态并传回DMA。在检测到SOF(Start Of Frame)时,MAC接收数据并开始MII发送。在EOF(End Of Frame)传输到MAC内核后,内核将完成正常的发送,然后将发送状态返回给DMA。

如果在发送过程中发送常规冲突,MAC内核将使发送状态有效,然后接受并丢弃所有后续数据,直至收到下一SOF。检测到来自MAC的重试请求时,应从SOF重新发送同一帧。如果发送期间未连续提供数据,MAC将发出下溢状态。在帧的正常传输期间,如果MAC在未获得前一帧的EOF的情况下接收到SOF,则将忽略该SOF并将新的帧视为前一帧的延续。

MAC控制MAC数据包的发送操作,它会自动生成前导字段和SFD以及发送帧状态返回给DMA,在半双工模式下自动生成阻塞信号,控制jabber(MAC看门狗)定时器用于在传输字节超过2048字节时切断数据包发送。在半双工模式下,MAC使用延迟机制进行流量控制,程序通过将ETH_MACFCR寄存器的BPA位置1来请求流量控制。MAC包含符合IEEE 1588的时间戳快照逻辑。

4.2.2 MAC数据包接收

MAC接收到的数据包填充RX FIFO,达到FIFO设定阈值后请求DMA传输。在默认直通模式下,当FIFO接收到64个字节或完整的数据包时,数据将弹出,其可用性将通知给DMA。DMA向AHB接口发起传输后,数据传输将从FIFO持续进行,直到传输完整个数据包。完成EOF帧的传输后,状态字将弹出并发送到DMA控制器。在Rx FIFO存储转发模式(通过ETH_DMAOMR寄存器中的RSF位配置)下,仅在帧完全写入Rx FIFO后才可读出帧。

当MAC在MII上检测到SFD时,将启动接收操作。MAC内核将去除报头和SFD,然后再继续处理帧。检查报头字段以进行过滤,FCS字段用于验证帧的CRC如果帧未通过地址滤波器,则在内核中丢弃该帧。

4.2.3 MAC过滤

MAC过滤功能可以选择性的过滤设定目标地址或源地址的MAC帧。它将检查所有接收到的数据帧的目标地址和源地址,根据过滤选择设定情况,检测后报告过滤状态。针对目标地址过滤可以有三种,分别是单播、多播和广播目标地址过滤;针对源地址过滤就只有单播源地址过滤。

单播目标地址过滤是将接收的相应DA字段与预设的以太网MAC地址寄存器内容比较,最高可预设4个过滤MAC地址。多播目标地址过滤是根据帧过滤寄存器中的HM位执行对多播地址的过滤,是对MAC地址寄存器进行比较来实现的。单播和多播目标地址过滤都还支持Hash过滤模式。广播目标地址过滤通过将帧过滤寄存器的BFD位置1使能,这使得MAC丢弃所有广播帧。

单播源地址过滤是将接收的SA字段与SA寄存器内容进行比较过滤。

MAC过滤还具备反向过滤操作功能,即让过滤结构求补集。

5. 官方例程及应用笔记(LWIP)

https://www.stmcu.org.cn/document/detail/index/id-213647

6. 硬件设计实例PHY: LAN8720A

AN8720A是SMSC公司(已被Microchip公司收购)设计的一个体积小、功耗低、全能型10/100Mbps的以太网物理层收发器。它是针对消费类电子和企业应用而设计的。LAN8720A总共只有24Pin,仅支持RMII接口.

LAN8720A通过RMII与MAC连接。RJ45是网络插座,在与LAN8720A连接之间还需要一个变压器,所以一般使用带电压转换和LED指示灯的HY911105A型号的插座。一般来说,必须为使用RMII接口的PHY提供50MHz的时钟源输入到REF_CLK引脚,不过LAN8720A内部集成PLL,可以将25MHz的时钟源陪频到50MHz并在指定引脚输出该时钟,所以我们可以直接使其与REF_CLK连接达到提供50MHz时钟效果。

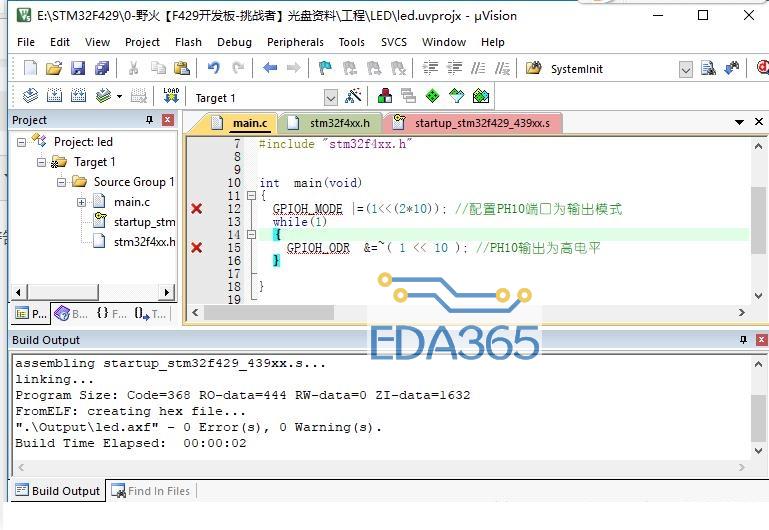

主要实现修改和实现以下文件

/**

* @brief ETH MAC Init structure definition

* @note The user should not configure all the ETH_InitTypeDef structure's fields.

* By calling the ETH_StructInit function the structure’s fields are set to their default values.

* Only the param

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多