1 引言

协议转换器的主要功能是接收调试服务器发来的各种调试协议信息,将它们转换成JTAG 时序信号,控制ARM 核以及EmbeddedICE 宏单元,并返回一些数据和状态信息给调试器。所以协议转换器主要由两部分组成:与调试器的通信接口部分,用于准确接收调试器发来的各种调试协议信息;与目标板的JTAG 接口部分,用于产生快速稳定的JTAG 时序信号。

各调试工具生产商所设计的协议转换器各不相同,但归纳起来主要有3种实现模型:

1.利用PC 的并口,外部加上简单的接口驱动电路或单片机引出JTAG 接口。这种实现模型的特点是价格便宜,没有固件程序或只有简单的固件程序,与调试器的接口单一,JTAG 时钟频率低,程序下载速度慢。网上流行的Wiggler 协议转换器和EasyJTAG 协议转换器就是基于这种实现模型。

2.利用单片复杂FPGA,实现与调试器的接口部分和产生快速JTAG 时序信号。这种实现模式的特点是价格昂贵,固件程序复杂,JTAG 时钟频率高,下载速度快。ARM 公司生产的Multi-ICE 协议转换器就是基于这种实现模型。

3.利用通用微处理器实现与调试器的接口部分,利用简单FPGA 或CPLD 产生快速JTAG 信号。这种实现模型是前两种实现模型的折中,价格适中,固件程序升级容易,与调试器的接口丰富,JTAG 时钟频率快,程序下载速度快。

本文介绍了使用ST72651设计实现协议转换器。利用ST72651 内部集成的USB模块和数据传输协处理器(DTC)分别实现与调试器的接口和JTAG 信号的稳定高速产生。这种实现方法属于第3 种模型,但微处理器模块和DTC 模块是封装在同一个芯片里面,这保证了微处理器模块和DTC 模块之间数据的快速传输。

2 硬件设计

2.1 ST72651 的概述

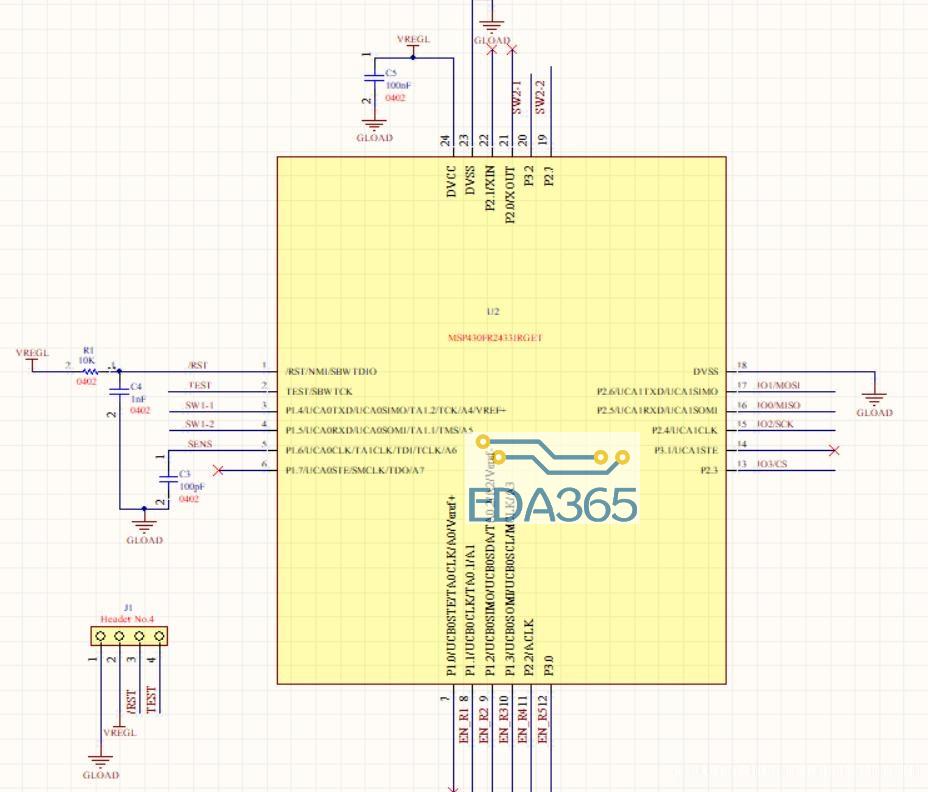

ST72651 是专门为解决USB 接口的大量数据传输应用而设计的一款芯片。它基于ST7标准内核,内部集成了一个全速的USB接口,以及一个时钟频率为24M 的数据传输协处理器(DTC),32KB 的程序存储空间,5KB 的RAM,支持I2C 和SPI 接口, 2.7V-5.5V 的工作电压范围,可用USB 接口直接供电,是一款功能强大的8 位机。

2.2 硬件原理框图

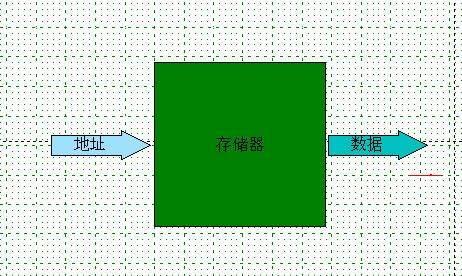

基于ST72651的协议转换器原理框图如图1所示。

图 1 协议转换器硬件原理框图

USB 接口部分的电路比较简单,只需在USB 的DP 脚上拉一个电阻,以使得USB 主机识别到该USB 设备。DTC 模块产生的4 个JTAG 时钟通过I/O 口引出,外部加一个接口驱动芯片,然后连到标准的JTAG接口上。TAP 控制器复位信号nTRST 和系统复位信号nSRST 通过I/O 逻辑直接控制。系统采用USB 供电模式,POWER 灯指示系统的供电状态。BUSY 灯连到TCK 引脚上,指示系统是否处于忙状态。内部集成的电压校准器产生3.3V 的电压供给接口驱动芯片。[page]

3 固件设计

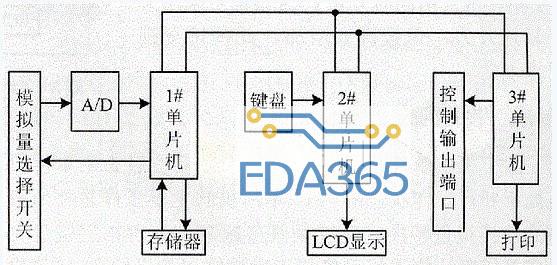

采用分模块设计固件程序,包括下列六个模块:DTC软件插件程序模块,扫描链操作模块,EmbeddedICE 寄存器操作模块,高层调试命令模块,USB接口驱动模块,主程序状态机模块。各模块的调用关系如图2所示。

图 2 固件各模块调用关系

3.1 DTC插件程序模块

ST72651内部集成的数据传输协处理器(DTC)是一个通用的串行/并行通信接口。ST7 核也可以读写DTC 的数据传输缓冲区,因此需要一个仲裁电路用于防止ST7核和DTC冲突访问该缓冲区。如果其中有一个在访问数据传输缓冲区,则另一个的请求将在数据传输缓冲区空闲时才得到响应;如果两个同时请求,则按优先级响应,ST7核的优先级高于DTC。ST7 核通过DTC 控制寄存器DTCCR 控制DTC的操作,通过DTC 状态寄存器DTCSR 查询DTC 的状态,通过DTC 指针寄存器DTCPR 改变DTC的操作指针。DTC功能框图如图3所示。

图 3 DTC功能框图

DTC运行的插件程序非常简单:将数据传输缓冲区中的数据快速移出到I/O口,或将I/O口数据快速移入到数据传输缓冲区。由DTC操作的I/O口为4个JTAG信号:TCK、TMS、TDI和TDO。TCK作为移入/移出数据的触发时钟,TDI作为移出数据出口,TDO 作为移入数据进口,TMS作为输入信号,与TCK 一起决定TAP 控制器状态的转移过程。执行插件程序前必须使TAP 控制器处Select-DR-Scan 状态,执行完插件程序后TAP 控制器返回到Select-DR-Scan状态。

3.2 扫描链操作模块

扫描链操作模块调用DTC 软件插件程序,完成初始化TAP 控制器、扫描链1操作和扫描链2操作。扫描链1有33位,按扫描先后顺序依次为:BREAKPT位(输入),D31-D0(输入/输出)。扫描链1 操作的目的是移入BREAKPT 位和向/从数据总线移入/移出 32位数据。扫描链2有38位,按扫描先后顺序依次为:EmbeddedICE 寄存器的D0-D31,EmbeddedICE 寄存器的A0-A4,读/写位。扫描链2 操作的目的是读写EmbeddedICE 宏单元的寄存器。[page]

3.3 EmbeddedICE寄存器操作模块

EmbeddedICE 寄存器的读写通过对扫描链2 操作实现。读时将欲读的EmbeddedICE 寄存器地址作为参数调用扫描链2 操作函数,写时将欲写的值和EmbeddedICE 寄存器地址作为参数调用扫描链2操作函数。

3.4高层调试命令模块

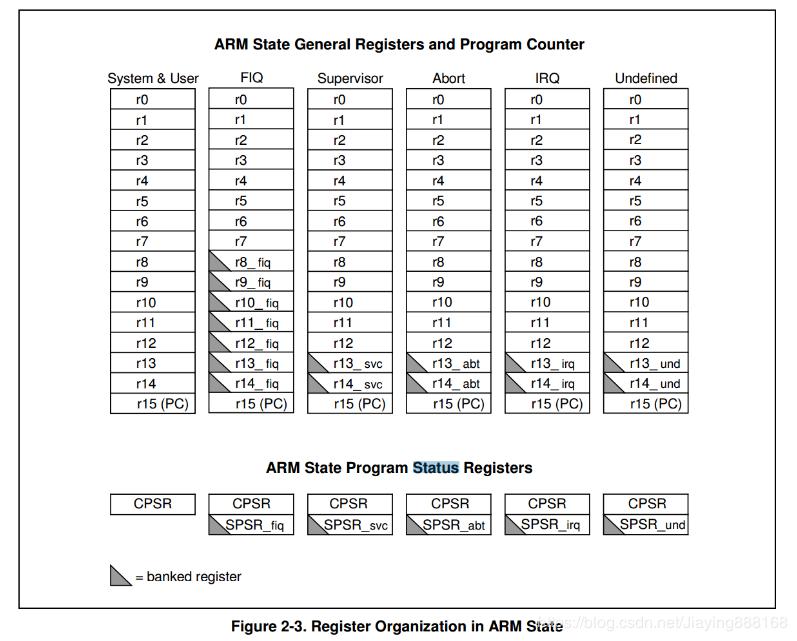

高层调试命令模块完成的功能是:调用扫描链操作模块和EmbeddedICE 寄存器操作模块,实现各种调试控制命令,这些命令供主程序状态机模块调用。包括下列调试控制命令:读写核寄存器,读写存储器,设置与清除硬件断点,设置与清除软件断点,设置与清除观察点,复位,停止运行,全速运行,单步运行,返回处理器状态,返回设备标志位。

3.5USB接口驱动模块

USB接口驱动模块主要包含五个函数:函数InitUSB( )用于初始化USB;函数USB_Polling( )用于处理USB 主机发来的USB 标准设备请求,实现USB 枚举阶段的传输过程,同时根据状态寄存器的标志位调用相应的端点处理函数;CTR中断服务程序用于处理端点上发生的各种中断;函数 USB_RecvDataEP2(unsigned char *dp, uint8 len)和USB_SendDataEP2(unsigned char *dp, uint8 len)分别用于从端点2接收和发送USB包。

ST72651内部集成的USB模块实现兼容USB2.0规范的全速(12Mb/s)USB协议。它包括:模拟收发器、3.3V 电压校准器、串行接口引擎(SIE)、USB 数据缓冲区接口、端点相关寄存器和各种控制状态寄存器,如图4所示。

图 4 USB功能模块

3.6 主程序状态机模块

主程序状态机模块循环调用USB 接口驱动模块的USB_RecvDataEP2( )函数接收调试器发来的命令报文,根据命令报文的主命令号和次命令号调用高层调试命令模块的相应命令函数,并将命令函数返回的数据通过调用USB_SendDataEP2( )函数返回给调试器,最终根据命令函数返回的状态通过调用USB_SendDataEP2( )函数发确认报文给调试器。

4 结束语

本文所设计的EmJTAG协议转换器代码下载速度、单步执行能力等各方面性能都接近ARM公司生产的Multi-ICE 协议转换器的性能。而EmJTAG支持USB接口协议与主机通信,在PC外围接口简化的今天,USB接口就大大方便了嵌入式软件设计者的使用,同时价格上的优势不言而喻的。该协议转换器实现与现成调试器AXD的连接,而ARM公司拥有调试器AXD的知识产权。为实现一个完整的自主产权ARM嵌入式软件开发工具链,还须完成的工作包括:自主产权编译系统的实现,自主产权主机调试器的实现。笔者希望本文对ARM调试系统在国内的研究和推广有所贡献。

本文作者创新点:本设计选取内部集成USB模块和数据传输协处理器(DTC)模块的微处理芯片。USB模块实现与调试器的通信,数据传输协处理器(DTC)模块产生稳定高速的JTAG 时序信号。微处理器模块和DTC 模块封装在同一个芯片里,这保证了微处理器模块和DTC 模块之间数据的快速传输。用封装在一块芯片上USB模块、微处理器模块和DTC 模块实现EmJTAG 协议转换器,以此协议转换器为理论基础的调试器非常方便、高速稳定和高性价比。

参考文献:

[1] 杨峰,张根宝等,基于JTAG的ARM芯片系统调试,微计算机信息,2005年,11-2:87-89

[2] ST,ST72651 DTC Specification,Jan. 2002

[3] 马忠梅等,ARM嵌入式处理器结构与应用基础,北京航空航天大学出版社,2002年1月

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多