(1)网口控制:实现网络通信,远程登录操作控制板,并接收外部的导航电文信息以及发送导航电文信息。

(2)串口控制:两个串行端口,一个用于计算机通过超级终端登录进行系统调试,另一个用于与发射单板的通信。LCD显示控制:显示信息的缓存。显示信息包括控制信息、告警信息,完成人机交互。

(3)键盘/按键控制:用于通过监测并接收键盘控制信息,传递给ARM处理器。

(4)系统工作状态监控:监测各单板的插入状态、工作温度及电源供电情况,并对各单板的供电进行控制;通过I2C总线与各单板进行通信,控制其他单板工作状态,下发控制指令。

(5)ISA总线控制:实现各芯片与ARM处理器之间的通信。

2 系统硬件设计

2.1 ARM微处理器的选择

S3C2440A的核心处理器(CPU)是一款由AdvancedRISC Machines公司设计的16/32位ARM920T的RISC处理器。它的特点具体如下:

(1)ARM920T内核实现了MMU,AMBA BUS和Harvard高速缓冲体系结构。这一结构具有独立16 kB的指令Cache和16 kB的数据Cache。且每个都是由8字长的行组成。

(2)片上由一个LCD控制器、3个通道的UART、4通道的DMA、2通道的SPI和1通道的IIC-BUS接口。

(3)支持NAND Flash系统引导、系统管理器。

(4)支持Thumb/ARM双指令集,能很好的兼容8位/16位器件,大量使用寄存器,寻址方式灵活简单,指令执行速度更快,效率更高。

(5)处理器主频最高可达400 MHz。

综上所述,S3C2440A微处理器的工作频率提高了系统的运行速度,使得处理器可以顺利地运行于Windows CE,Linux等操作系统以较为复杂的信息处理,可减少软件开发时间;S3C2440A具有强大的内部中端,方便进行TCP/IP的轮询调用;S3C2440A具有丰富的外围设备资源,可简化微微电路中的扩展部分,降低系统的复杂度、减少系统成本。所以选S3C2440A作为该系统的核心处理器。[page]

2.2 辅助控制模块电路设计

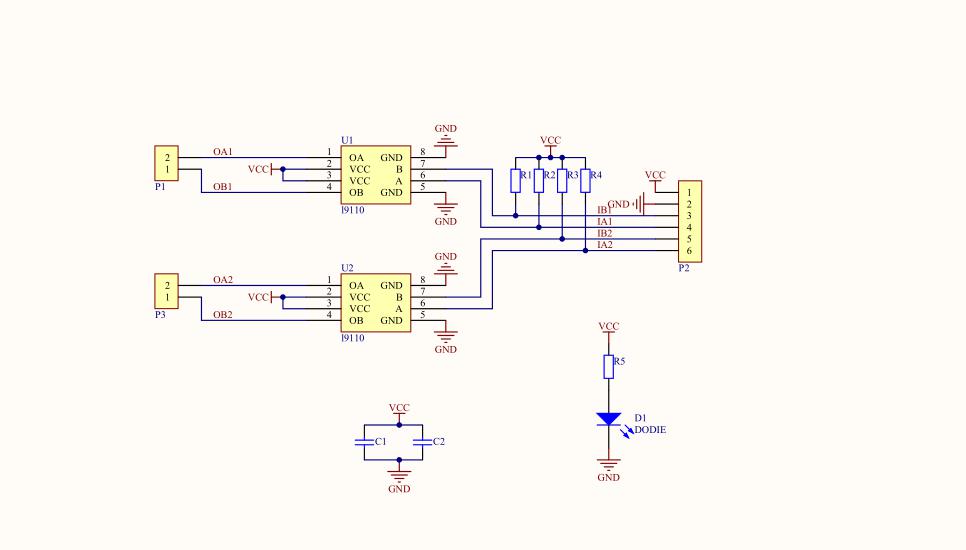

系统使用的FPGA型号为Xilinux公司生产的Spartan XCS30,其完成各个器件与外接设备之间的检测和监控。FPGA XCS30所要实现的功能:接收从键盘按键模块传输的操作信息,并把接收到的信息发送到控制芯片进行处理,同时接收从控制芯片生成的状态信息,FPGA XCS30还可控制面板上的LED灯显示。

FPGA与S3C2440A使用ISA总线连接通信,如图2所示。在S3C2440A BIOS设置中将“AdditionalISA I/O area 1”设置为“Enabled”,允许使用400h地址以上的ISA I/O空间,CPU可直接对该空间I/O访问。将“Base Address”设置为“8200h”,“Range(bytes)”设置为“51 2”。在程序资源中可为FPGA分配从8200h起的连续512个I/O地址。

FPGA XCS30使用具有主菜单、取消、确认、上、下、左、右和本地控制的8键位键盘,具有Power(+5)、Power(-5)、Error、Open、Local的5个LED显示灯。其寄存器地址8244h作为键盘和LED共同使用的寄存器地址,对于S3C2440A而言,键盘状态为读操作,LED状态为写操作。数据交换使用8 bit I/O读写。

2.3 LCD接口电路设计

在控制单元中,外接设备LCD作为系统人机交换界面,起着重要作用。其显示包括系统操作菜单、系统运行状态和系统工作参数等信息,并且可以实时显示键盘所进行的参数设定,状态设定等功能。系统中外接设备LCD使用的是Powertip公司生产的PC4002LRU LCD。

S3C2440A具有支持LCD的引脚,可以直接与PC4002进行连接,而且其BIOS中已经嵌套配置支持LCD,如图3所示。在物理链接上控制板与LCD通过背板进行信号通信。使用8 bit I/O读写进行数据交换。PC4002使用并行端口连接,占用从0X378h开始的8个I/O寄存器,其中0378h作为数据寄存器,0379h作为状态寄存器,037A作为控制寄存器。[page]

3 系统软件设计

系统的软件部分是在Linux操作系统下实现的。结合控制系统的功能分为人机交互、参数设定、电文处理、远程控制4个模块,图5为软件设计流程图。

[page]

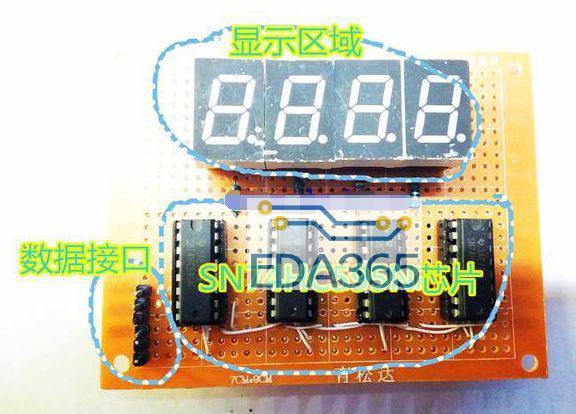

(1)人机交互模块。通过LCD设备提供系统的操作菜单显示,利用键盘操作完成用户的直接操作,同时利用机箱前面板上的LED指示灯向用户显示系统的工作状态。S3C2440A处理器接收从FPGA传送来的由键盘生成的相应控制指令,判断控制指令并且根据控制指令更改操作菜单、参数设定、状态信息。在液晶显示器上实时显示系统的状态信息和参数信息等,以保证正常的人机交互,如图6所示。

(2)参数设定模块。根据人机交互模块判断的控制指令设定系统的工作参数,通过RS-232收发器完成控制单元与GSG单板进行通信,将保存的导航电文发送到GSG单板的FPGA中,进行参数设定和改变发射状态。

(3)电文处理模块。通过以太网MAC控制器DM9000与外部主机进行网络通信,接收导航电文,在控制RS-232收发器与GSG单板进行通信,将收到的导航电文发送到GSG单板的FPGA中进行调制。如图7所示为得到GSG产生的在S码的波形图。

(4)远程控制模块。远程控制服务通过网络完成,用户可以使用计算机超级终端程序,连接时间同步仪对其进行控制。利用远程客户端,经过身份识别后获得对时间同步仪的控制权,从而进行参数设定、工作状态设定等操作。图8所示为远程控制界面。

4 结束语

采用S3C2440A为主控制单元,FPGA为辅助控制单元,实现了时间同步仪控制单元的设计要求:人机交互模块实现了键盘控制,LCD显示以及多级菜单功能。参数设定模块通过改变状态得到了相应的波形图结果。电文处理通过注入电文与GSG单板FPGA引出信号比对测试,验证了电文处理的正确性。远程控制模块通过Telnet软件测试得到了预期的控制结果。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多