RC(Reset and Clock Control)复位和时钟控制

STM32F10x支持三种复位形式,分别为系统复位、上电复位和备份区域复位。

系统复位将复位除时钟控制寄存器CSR中的复位标志和备份区域中的寄存器以外的所有寄存器。

当以下事件中的一件发生时,产生一个系统复位:

1. NRST管脚上的低电平(外部复位)

2. 窗口看门狗计数终止(WWDG复位)

3. 独立看门狗计数终止(IWDG复位)

4. 软件复位(SW复位)

5. 低功耗管理复位

可通过查看RCC_CSR控制状态寄存器中的复位状态标志位识别复位事件来源。

软件复位

通过将Cortex?-M3中断应用和复位控制寄存器中的SYSRESETREQ位置’1’,可实现软件复位。

低功耗管理复位

在以下两种情况下可产生低功耗管理复位:

1. 在进入待机模式时产生低功耗管理复位:

通过将用户选择字节中的nRST_STDBY位置’1’将使能该复位。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

2. 在进入停止模式时产生低功耗管理复位:

通过将用户选择字节中的nRST_STOP位置’1’将使能该复位。

这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式。

电源复位

当以下事件中之一发生时,产生电源复位:

1. 上电/掉电复位(POR/PDR复位)

2. 从待机模式中返回

电源复位将复位除了备份区域外的所有寄存器。

备份区域拥有两个专门的复位,它们只影响备份区域。

备份域复位

当以下事件中之一发生时,产生备份区域复位。

1. 软件复位,备份区域复位可由设置备份区域控制寄存器RCC_BDCR中的BDRST位产生。

2. 在VDD和VBAT两者掉电的前提下,VDD或VBAT上电将引发备份区域复位。

HSE(High Speed External)高速外部时钟信号

在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定。

在启动时,直到这一位被硬件置’1’,时钟才被释放出来。

如果在时钟中断寄存器RCC_CIR中允许产生中断,将会产生相应中断。

HSE晶体可以通过设置时钟控制寄存器里RCC_CR中的HSEON位被启动和关闭。

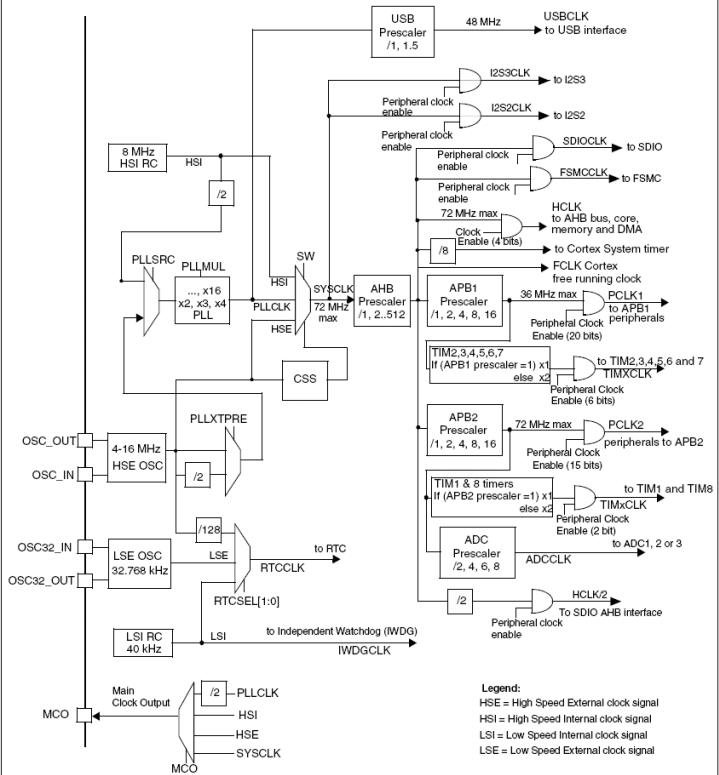

时钟

三种不同的时钟源可被用来驱动系统时钟(SYSCLK):

● HSI振荡器时钟

● HSE振荡器时钟

● PLL时钟

这些设备有以下2种二级时钟源:

● 40kHz低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC。

RTC用于从停机/待机模式下自动唤醒系统。

● 32.768kHz低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK)。

当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗。

HSI(High Speed Internal)高速内部时钟信号

HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL输入。

HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟。

它的启动时间比HSE晶体振荡器短。然而,即使在校准之后它的时钟频率精度仍较差。

系统复位时,工厂校准值被装载到时钟控制寄存器的HSICAL[7:0]位。

如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度。

你可以通过利用在时钟控制寄存器里的HSITRIM[4:0]位来调整HSI频率。

时钟控制寄存器中的HSIRDY位用来指示HSI RC振荡器是否稳定。

在时钟启动过程中,直到这一位被硬件置’1’,HSI RC输出时钟才被释放。

HSI RC可由时钟控制寄存器中的HSION位来启动和关闭。

如果HSE晶体振荡器失效,HSI时钟会被作为备用时钟源。

PLL(Phase Locking Loop)锁相环路

内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟。

PLL的设置(选择HIS振荡器除2或HSE振荡器为PLL的输入时钟,和选择倍频因子)

必须在其被激活前完成。一旦PLL被激活,这些参数就不能被改动。

如果PLL中断在时钟中断寄存器里被允许,当PLL准备就绪时,可产生中断申请。

如果需要在应用中使用USB接口,PLL必须被设置为输出48或72MHZ时钟,用于提供48MHz的USBCLK时钟。

LSE(Low Speed External)低速外部时钟信号

LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器。

它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源。

LSE晶体通过在备份域控制寄存器(RCC_BDCR)里的LSEON位启动和关闭。

在备份域控制寄存器(RCC_BDCR)里的LSERDY指示LSE晶体振荡是否稳定。

在启动阶段,直到这个位被硬件置’1’后,LSE时钟信号才被释放出来。

如果在时钟中断寄存器里被允许,可产生中断申请。

LSI(Low Speed Internal)低速内部时钟信号

LSI RC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟。

LSI时钟频率大约40kHz(在30kHz和60kHz之间)。

LSI RC可以通过控制/状态寄存器(RCC_CSR)里的LSION位来启动或关闭。

在控制/状态寄存器(RCC_CSR)里的LSIRDY位指示低速内部振荡器是否稳定。

在启动阶段,直到这个位被硬件设置为’1’后,此时钟才被释放。

如果在时钟中断寄存器(RCC_CIR)里被允许,将产生LSI中断申请。

SYSCLK(System Clock)系统时钟选择

系统复位后,HSI振荡器被选为系统时钟。

当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止。

只有当目标时钟源准备就绪了(经过启动稳定阶段的延迟或PLL稳定),从一个时钟源到另一个时钟源的切换才会发生。

在被选择时钟源没有就绪时,系统时钟的切换不会发生。直至目标时钟源就绪,才发生切换。

在时钟控制寄存器(RCC_CR)里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟。

CSS(Clock Security System)时钟安全系统

时钟安全系统可以通过软件被激活。

一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭。

RTC(Real Time Clock)实时时钟

通过设置备份域控制寄存器(RCC_BDCR)里的RTCSEL[1:0]位,RTCCLK时钟源可以由HSE/128、LSE或LSI时钟提供。

除非备份域复位,此选择不能被改变。LSE时钟在备份域里,但HSE和LSI时钟不是。

看门狗时钟

如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭。

在LSI振荡器稳定后,时钟供应给IWDG。

时钟输出

微控制器允许输出时钟信号到外部MCO管脚。

相应的GPIO端口寄存器必须被配置为相应功能。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多