一、实验目的

熟悉利用QuartusⅡ的图形编辑输入法设计简单组合电路,掌握层次化设计方法,并通过8位全加器的设计,进一步熟悉利用EDA软件进行数字系统设计的流程。

二、实验仪器与器材

计算机1台,GW48-PK2S实验箱1台,QuartusⅡ6.0 1套。

三、实验内容

1. 基本命题

利用图形输入法设计一个一位半加器和全加器,再利用级联方法构成8位加法器。

2. 扩展命题

利用文本输入法设计4位并行进位加法器,再利用层次设计方法构成8位加法器。通过时序仿真,比较两种加法器的性能。

四、实验设计思路

按照如图2-1,2-2,2-3设计半加器、全加器、串行级联加法器

① 设计半加器

图2-1半加器设计图

② 设计全加器

图2-2全加加器设计图

③ 设计串行级联8位加法器

图2-3串行级联8位加法器设计图

④ 仿真波形图

对以上的串行级联加法器进行仿真。设置时钟频率为/1/10ns。每20ns对a,b输入口进行+2操作。所得结果见图2-8。由图可知延时大约为14ns。

图2-4串行级联加法器仿真波形图

对以上的串行级联加法器进行仿真。设置时钟频率为/2.0us。每10us对a,b输入口进行+2操作。所得结果见图2-4。由图可知延时大约为10us。

五、实验要求

将实验原理、设计过程、编译仿真波形和分析结果、硬件测试实验结果写进实验报告。

六、实验思考题

(1)与单一设计文件比较,实现层次化设计应注意哪些问题?

答:实现层次化设计需要注意的是:假设B设计中引用A设计,那么需要将A设计的工程文件放在B设计的工程文件中,另外,B设计的工程必须要以B的实体名称对应,不然仿真的时候会出错。

(2)比较图形编辑和文本编辑两种8位二进制加法器的性能,分析它们的主要异同点。以下是文本编辑的参考程序。

1) 4位二进制数加法器ADDER4B的VHDL描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ADDER4B IS

PORT ( CIN4 : IN STD_LOGIC;

A4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

S4 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT4 : OUT STD_LOGIC);

END ADDER4B;

ARCHITECTURE behav OF ADDER4B IS

SIGNAL SINT : STD_LOGIC_VECTOR(4 DOWNTO 0);

SIGNAL AA,BB : STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

AA<='0'&A4;

BB<='0'&B4;

SINT <= AA + BB + CIN4;

S4 <= SINT(3 DOWNTO 0);

COUT4 <= SINT(4);

END behav;

图2-9ADDER4B仿真波形图

对以上的ADDER8B进行仿真。设置时钟频率为/2.0us。每10us对a,b输入口进行+2操作。所得结果见图2-9。由图可知延时大约为20us。

2)应用ADDER4B设计8位二进制数加法器ADDER8B的VHDL描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ADDER8B IS

PORT ( CIN : IN STD_LOGIC;

A : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

COUT : OUT STD_LOGIC );

END ADDER8B;

ARCHITECTURE struc OF ADDER8B IS

COMPONENT ADDER4B

PORT ( CIN4 : IN STD_LOGIC;

A4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

S4 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT4 : OUT STD_LOGIC );

END COMPONENT;

SIGNAL CARRY_OUT : STD_LOGIC;

BEGIN

U1 : ADDER4B -- 例化一个4位二进制加法器U1

PORT MAP ( CIN4 => CIN, A4 => A(3 DOWNTO 0),

B4 => B(3 DOWNTO 0), S4 => S(3 DOWNTO 0),

COUT4 => CARRY_OUT );

U2 : ADDER4B --例化一个4位二进制加法器U2

PORT MAP ( CIN4 => CARRY_OUT, A4 => A(7 DOWNTO 4),

B4 => B(7 DOWNTO 4), S4 => S(7 DOWNTO 4),COUT4 => COUT );

END struc;

图2-10ADDER8B仿真波形图

对以上的ADDER8B进行仿真。设置时钟频率为/2.0us。每10us对a,b输入口进行+2操作。所得结果见图2-10。由图可知延时大约为20us。

实验错误小结:

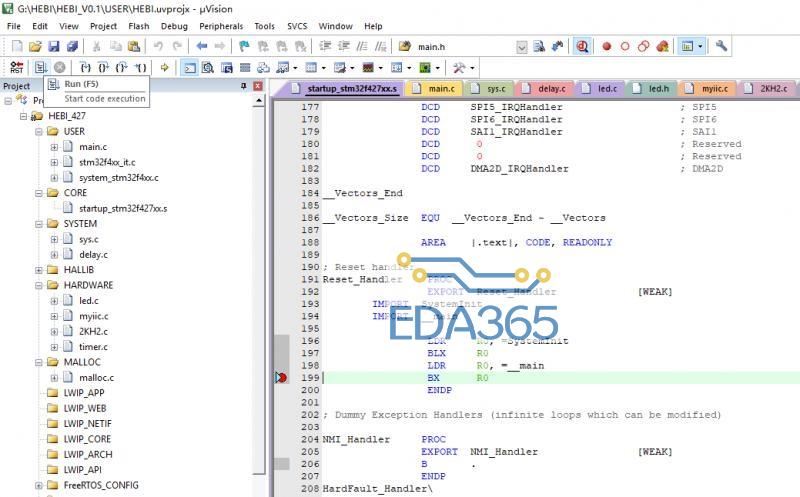

Quartus中仿真时出现no simulation input file assignment specify 解决方法

这个错误的意思是:仿真文件没有被指定,要仿真的话先要建一个仿真文件:

情况1、file -> new -> 选择Other file选项卡 -> Vector Waveform File

然后把输入输出端口加进去,再设置输入的信号,保存,就可以仿真了。

情况2、如果你之前已经建立过了,就打开assignments->settings->simulator settings

看里面的有个文本框 simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VMF结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project里面找到。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多