刚开始学习5438,感觉这款单片机的时钟模块特别灵活,也是为了低功耗而设计的。但是灵活的代价是使得对时钟模块的操作复杂化了。我研究了很久终于略微懂了些,写出来希望能帮到和我一样的初学者。

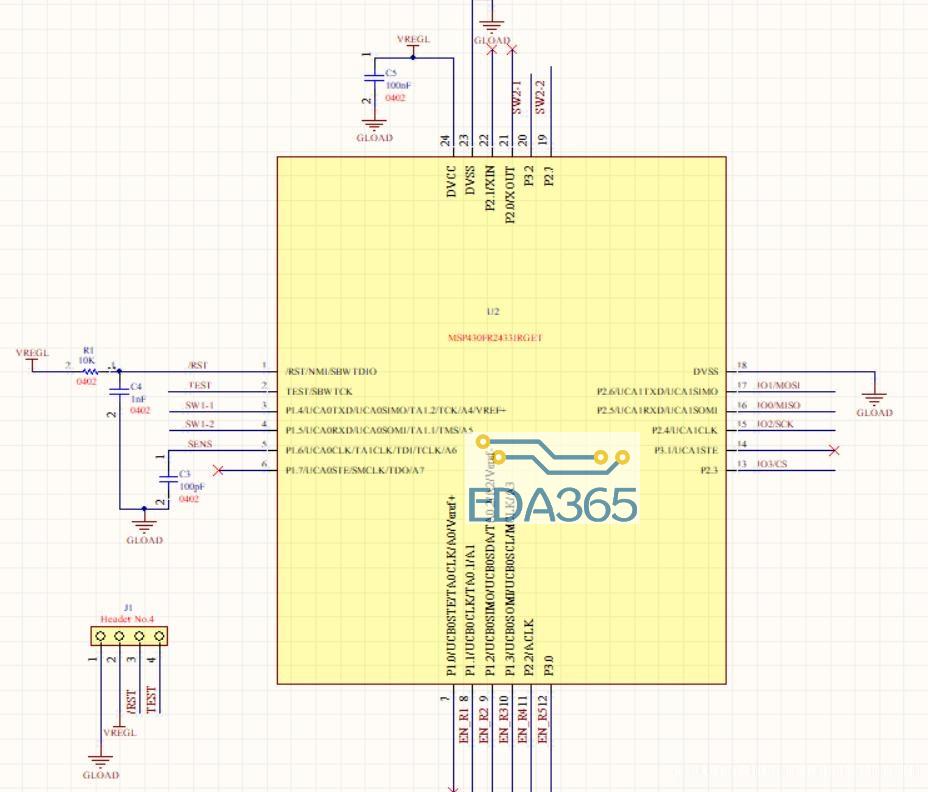

所有的答案都在这一张图上了,这张图我看了很久,方向是我后来加上的。如果你想灵活使用它的时钟,这张图一定好好看看。

时钟源有六个,就是那六个红色的箭头,经过选择最终可以提供三个时钟信号ACLK,MCLK,SMCLK。

这个图主要部分有三块,我们分别来看:

OSC

首先是时钟源的选择,可以使用32768Hz的手表晶振、标准晶体、谐振器或4—16Mz的外部时钟源。

通过XT1BYPASS(由寄存器UCSCTL6中设置)可以选择是晶振或谐振器还是外部时钟源。

当XT1BYPASS为1时XT1CLK选择外部时钟源。为0时选择为晶振或谐振器,此时还需要设置XTS、XCAP、XT1DRIVE(寄存器UCSCTL6中)。

XTS为0时工作在低频模式下,设置XCAP为晶振选择内部负载电容。XTS为1时工作在高频模式下,支持高频晶振,但要在XIN和XOUT引脚上接外部负载电容。

XT1DRIVE用于设置驱动能力。以使XT1快速启动和支持不同频率的晶振或振荡器。

内部VLO 在无需外部晶振的情况下提供12kHz 的典型频率,VLO为对时钟要求不高的应用系统提供了低成本、超低功耗的时钟源。当VLO 被用作ACLK、MCLK 或 SMCLK 时(SELA=1SELM=1或SELS=1),VLO被选中。

REFO为内部调整低频参考时钟振荡器,在不要求或不允许使用晶振的应用中,REFO可以用作高灵敏时钟。REFO是内部调整过的32768Hz 时钟,提供一个稳定的参考时钟用作FLLREFCLK。REFOCLK 与 FLL 组合在无需外部晶振的情况下提供灵活的大范围的系统时钟。不使用REFO时,REFO不消耗电源。

FLL

这一块是比较难懂的了。待我细细分析。

FLL模块的核心是DCO振荡器、DCO频率调节器和一个十位的频率积分器。

DCO振荡器由DCORSEL(UCSCTL1中)的三个控制位选择8 个标称频率范围中的一个。DCO的5个控制位将由DCORSEL 位选择的DCO 频率范围分成32 等份,间隔大约为8%。具体参数参见手册。

MOD的5个位,使频率在DCOx 和下一个频率DCOx+1 之间转换。采用32周期调制法,32个周期中有MOD个周期的频率是 。当 DCO=31 时,MODx 位功能失效,因为此时DCO的频率已经是DCORSEL位选择的频率范围的最高频率了。操作过程如下图所示:

由于DCO的频率会受温度以及电压的影响,所以为了保持频率稳定,通过了频率积分器产生一个十位的偏差。FLLREFCLK/FLLREFDIV使积分器加1,DCOCLK/FLLD/(N+1)使积分器减1.积分器通过这个偏差调整DCOCLK的频率。形成一个调整反馈环。

FLLREFCLK的来源有三个,分别是XT1CLK、REFOCLK和XT2CLK。通过设置SELREF(UCSCTL3中)来选择。

如果状态寄存器SR中的SCG0和SCG1位为1时,FLL被禁止,DCO以预先选择的频拍运行且不会自动稳定。 当DISMOD被置位时DCO调制器被禁止,DCOCLK被调整到由DCO位选择的的DCO频率上。

XT2

XT2模块和OSC模块类似,但比它简单些,主要应用于对时钟要求较高的情况。

UCS模块寄存器

UCS模块共有10个寄存器,但是很多位都是保留的,具体用到的不是很多。可以结合上面的结构图对寄存器进行设置,初始化值在图中有表示。

系统初始化

系统复位后系统的初始化如下:

XT1处于LF(低频)模式且被选为XT1CLK时钟源。

ACLK被选作 XT1CLK

MCLK选择DCOCLKDIV

SMCLK选择DCOCLKDIV

FLL操作使能,XT1CLK作为FLL的参考时钟FLLREFCLK

XIN和XUOT被设置为普通I/O,XT1失效

XT2IN和XT2UOT被设置为普通I/O,XT2失效

由于XT1失效所以会产生时钟错误,而ACLK和FLLREFCLK都是选择XT1CLK作为时钟源,此时错误控制逻辑会使ACLK和FLLREFCLK选择REFOCLK。DCOFFG和XT1LFOFFG默认为置位状态,使用时必须先清除错误标志.

以上是手册中的内容,下面是我的疑惑:

1、为何不把XIN和XOUT对应的引脚初始化设置为晶振接口,这样就省去了产生错误之后再转换时钟的麻烦。或者是把ACLK和FLLREFCLK直接选择REFOCLK。

2、产生时钟错误时,手册上说会通过错误控制逻辑自动切换时钟源,但是没有改变时钟选择位SELx,需要在用户程序中操作。但不知道是怎样的原理。不知道如果程序中不改变控制位会是什么情况。

当时钟刚打开或没有正常工作时晶体振荡器错误标志位XT1LFOFFG,XT1HFOFFG或XT2OFFG相应的位将被置位,一旦被置位即使已经恢复正常状态也将一直保持置位。如果还存在错误时用户用软件将错误标志位清零,则错误标志位将自动置位,否则将保持清零。

时钟运行在除LF模式下的XT1时,如果发生时钟错误ACLK、MCLK、SMCLK都自动转换选择DCOCLKDIV。而工作在XT1的LF模式下时,三个时钟都会切换为REFOCLK。但是选择位SELx不会改变,需要由用户程序操作。

关键字:MSP430 时钟模块 UCS『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多