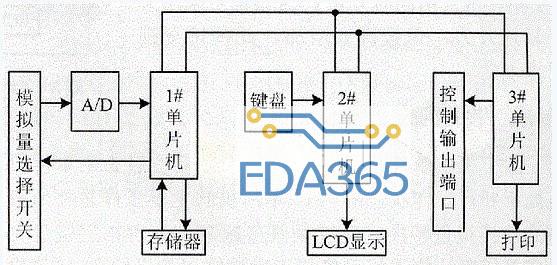

1 系统总体设计

CY7C136是2 KB高速CMOS静态RAM。同一片RAM上有2组数据线和2组地址线,对每个端口的控制是相互独立的,可分别在存储器的任意位置存取数据。

双口RAM作为2个MCU的共享资源,一个端口与MCUl相连,另一个端口与MCU2相连。从SJAlOOOCAN总线接口1接收来的数据送入双口RAM,这些数据被MCU2取走并送到SJAl000 CAN总线接口2上;从SJAl000 CAN总线接口2接收来的数据也送入双口RAM,并被MCUl取走送到SJAl000 CAN总线接口1上。由于MCU的地址总线和数据总线是复用的,因此采用锁存器进行地址锁存,硬件总体结构如图1所示。

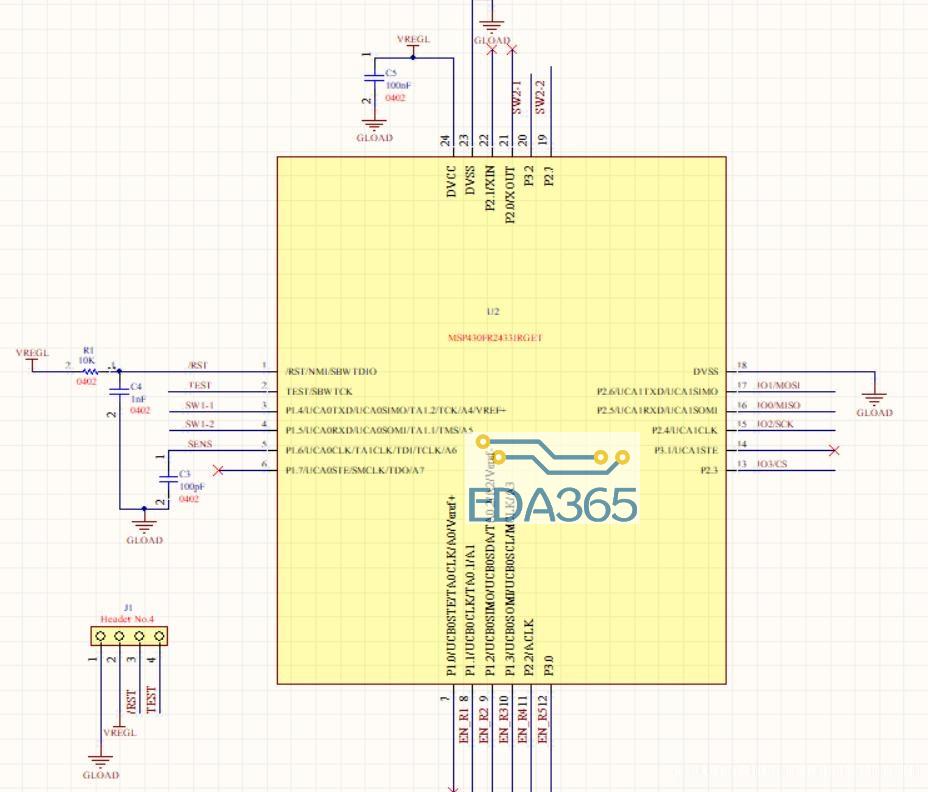

2.2 双口RAM接口电路

双口RAM电路接口如图3所示。双口RAM芯片CY7C136作为2个MCU数据的中转站,分别与2个MCU的相应引脚相连。其中CY7C136引脚I/O0L~1/O7L与第1片AT89C52(MCUl)的PO相连,引脚I/OOR~I/O7R与第2片AT89C52(MCU2)相连。YOAOUT为MCU1读写双口RAM的片选信号,Y1AOUT为MCU2读写双口RAM的片选信号,并将MCU的读写控制信号线与双口RAM的相应读写控制信号线相连。

3 软件设计实现

3.1 存储空间分配思想

为使双口RAM实现最高效率的应用,将2 KB的存储空间设计成2个1 KB大小的环形队列形式,每一个环形队列的结构如图5所示(图中阴影部分为存有数据的区域,非阴影区域为空闲区域)。

4 测 试

对基于双口RAM的双MCU中继器进行压力测试(高数据负载率下测试)。短距离内向2个CAN口加载10 000帧数据,测试中继器成功中转情况,其结果如表1所列(表身数据为成功中转帧数)。根据CAN总线规定,其平均负载率不超过65%,传统的单MCU CAN中继器平均负载率很难达到60%。从表1可以看出,引入双MCU后CAN中继器的性能大大提高,能在负载率超过60%的情况下稳定工作。环形队列queue溢出的情况可以通过增加双口RAM的大小来解决。

结 语

采用双MCU配合双口RAM设计CAN总线中继器,解决了单MCU无法快速处理CAN总线负载过重的问题,使其性能和效率得到了很大提高,为CAN中继器在工程领域的优化设计提供了良好的技术平台和解决方案。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多