根据国外媒体报道,东芝日前开发出一种新型触发器电路,使用CMOS工艺,可以有效降低移动设备中的功耗。

“数据显示,该新触发器的功耗较传统触发器降低约77%,而采用该技术的无线局域网芯片的总功耗降低了24%。”根据东芝公司的声明。

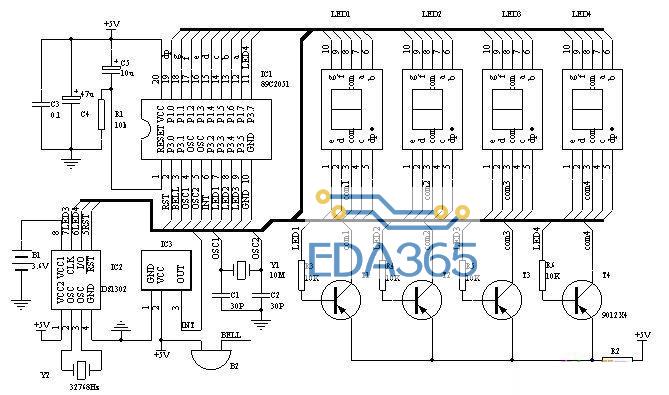

触发器是一种可以存储电路状态的电子元件。最简单的是由两个或非门,两个输入端和两个输出端组成的RS触发器。复杂一些的有带时钟(CLK)段和D(Data)端,在CLK端为高电平时跟随D端状态,而在CLK端变为低电平的瞬间锁存信号的D触发器。更常用的是两个简单D触发器级联而成的在时钟下跳沿锁存信号的边缘D触发器,广泛应用于计数器、运算器、存储器等电子部件。在一个典型的SoC芯片中,需要有10万至1000万个触发器。

触发器一般都带有时钟缓冲器,而东芝则改变了触发器结构,消除了时钟缓冲器的能耗。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多