SoC的设计步伐变得越来越快了,Magma公司产品市场部副总裁Bob Smith举例道,“2007年的iPhone处理器主频为620MHz,内存为128Mb,而2010年,iPhone4的主频已经到了800MHz以上,内存也增加至512Mb。”

Smith表示,目前SoC设计团队存在着“三座大山”,包括设计费用,设计效率以及复杂性和技术的挑战。

Robert (Bob) Smith

市场副总裁

设计实现业务部

微捷码设计自动化有限公司

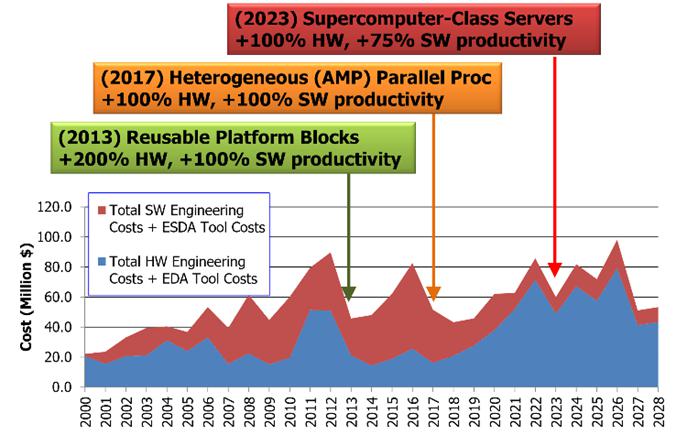

麦肯锡2009年报告中指出,伴随着节点演进,设计费用将大笔攀升,130nm时设计费用是1000至1500万美元,而到了32nm,技术提高了4个节点而费用也相应了提升了360%即6000至7000万美元。而节点演进,芯片中晶体管数量亦成倍增加,从65nm时的40亿个增长至22nm时的320亿个,这就给设计带来了极大地挑战。Smith举例道,在22或18nm时,模增加到15个,而角会增加到50个。

另外一份《半导体国际技术蓝图》中指出,2009年每个设计人员每年大概需120万门左右的设计工作量,而到了2021年将达到3200万个,显然如果在工具上没有突破的话,是不能能完成如此高效率的工作的。

从最早的BlastFusion起,Magma就专注于数字设计领域,而后虽转向模拟混合信号设计,但Magma最近在纯数字领域又开始加速其技术进程,包括时序分析Tekton以及近期推出的IC设计解决方案Talus 1.2和分布式IC设计解决方案Talus Vortex FX。

Talus 1.2系统让工程师能够在考虑串扰规避、高级片上变异和多模多角分析的情况下,以每天一百只一百五十万单元的处理能力完成二百至五百万单元规模的设计或模块的实现。目前Talus已通过40纳米节点芯片的验证,现同时应用于复杂的28纳米设计,而对于20及20纳米以下的设计问题也已有了万全准备。

Talus 1.2主要包括如下功能:

·Talus MX布线器(Talus MX Router) – 提供增强的全局、轨道和详细布线功能以及贯穿整个流程的时序收敛,消除DRC违规。

·Talus MX时序器(Talus MX Timer) – 基于微捷码下一代签核时序分析技术,实现了更快速精确的时序分析。

·Talus MX提取器(Talus MX Extractor) – 基于微捷码最新的高速、多角提取技术,提供更快速精确的提取。

·并发多模多角优化(Concurrent MMMC optimization) – 管理较传统解决方案多5倍的时序情景,提供了10倍的运行时间改善。

·高级片上变异(Advanced On-Chip Variation,AOCV)– 确保贯穿整个流程的紧密时序一致性。

·串扰规避(Crosstalk Avoidance)– 优化和实施期间检测并纠正串扰规避。

Talus Vortex FX则是业界首款分布式IC实现管理解决方案,基于Talus 1.2的功能而创建,提供了更高的容量及多达3倍的吞吐量。Talus Vortex FX的分布式智能同步技术实现了重大的技术突破,可横跨整个网络的设备进行超大型设计的并发实现管理与智能同步,从而让设计师即便面对尺寸更大得多的电路模块也能够充分进行优化,显著缩短了设计周期。

Talus Vortex FX可以实现现有软硬件资源的有效使用。Talus 1.2的智能内存使用技术允许Talus Vortex FX运行于各种标准服务器平台上,一般是配置为4-8个处理器核心和64 GB内存的平台。此外,Talus Vortex FX还能够利用可能闲置的现有Talus 1.2许可。

相关白皮书下载,请访问:http://www.eeworld.com.cn/magma/2010/1208/down_40.html

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多