随着芯片设计越来越复杂,原型验证变得更为重要已经成为了共识,Synopsys 资深产品市场经理Neil Songcuan表示,当下物理原型解决方案面临着诸多挑战:如何映射到FPGA、能见度、性能、容量以及周转时间等。

Synopsys日前推出全新HAPS®-80基于FPGA的原型系统,该系统为Synopsys的端到端原型解决方案的一部分。HAPS-80系统提供了高达100MHz的多FPGA性能,以及全新的专用高速时分复用(HSTDM)技术。HAPS-80采用Xilinx最新的Virtex UltraScale VU440 FPGA器件,每颗FPGA可容纳2600万个ASIC门,结合ProtoCompiler设计自动化和调试软件,可支持高达16亿个ASIC门的设计。同样的也和以前的HAPS产品相兼容,子板等产品都通用,客户并不会产生额外的投入。

Synopsys官方表示,采用HAPS-80可将原型验证时间缩短至两周内,这种效率的显著提升是各种技术改进综合的结果。

通过总是可用的第四代深度追踪调试技术(HAPS DTD4, HAPS Deep Trace Debug Gen4),HAPS-80系统提供了出色的调试可见度和自动化技术,通过它可在运行时从每个FPGA捕获超过1000个调试信号位。HAPS-80系统内置了调试数据采集、存储器和专用路由,且它们由ProtoCompiler自动插入以确保最小的干预,总是对用户可用。与Synopsys的Verdi™调试软件结合,HAPS DTD4可帮助设计人员以仿真器般的经验在原始RTL源文件的语境中,快速地辨识复杂的设计行为,使调试时间缩短多达50%。此外,HAPS和ProtoCompiler结合Verification Continuum的Unified Compile技术,使得在Synopsys VCS®仿真、ZeBu®模拟和HAPS原型之间移植更容易,从而可为设计和验证节省数月时间。

通用多源总线(UMRBus)的主机连接能力支持混合原型验证、全球可访问和大型原型群等使用模式。UMRBus在HAPS-80系统和Synopsys基于Virtualizer的虚拟原型之间无缝连接,为早期软件开发和硬件/软件集成创造了一种集成化的混合原型验证环境。此外,HAPS-80可向下兼容HAPS-70,让设计人员可复用现有的系统和硬件配件。对原生以太网连接的支持,使HAPS-80系统通过标准以太网连接便可实现系统的全球可访问。HAPS-80解决方案支持多设计模式,在企业配置中,可跨HAPS系统同时执行多个设计,为多项目用途提供最高的原型利用率及更高的投资回报率。

HAPS硬件与ProtoCompiler软件的结合,极大地加速了软件开发、硬件/软件集成和系统验证。ProtoCompiler从IP到SoC的层次化流程,将RTL、设计原型约束、预定义的调试可观测点和逻辑综合指示封装在一起,以消除在SoC中重复这些任务的需求,将集成时间缩短了数周。软硬件无缝结合,这也是Synopsys所说的端到端的原型设计整体方案。

Xilinx测试、测量和仿真市场业务部总监HannekeKrekels表示。“UltraScale芯片的器件密度提升了2.2倍,I/O增加了21%,它对于使用HAPS系统来实现多FPGA分区的复杂SoC原型是非常理想的。”

ProtoCompiler利用HAPS-80的全新HSTDM功能,自动选择引脚时分复用最优组合方案,可与待测设计最佳地匹配。HAPS-80集成解决方案,对于单FPGA设计性能可高达300MHz;在不使用引脚时分复用的情况下,多FPGA设计性能可高达100MHz;在使用全新专有高速引脚时分复用的情况下,多FPGA设计性能可超过30MHz。HAPS-80系统性能的提升,使得操作系统不到一分钟便可启动到命令提示符,让设计人员能够探测和初始化硬件设备,如CPU、定时器和通用异步接收发送器(UART)等。HAPS-80也支持真实世界I/O全速运行。

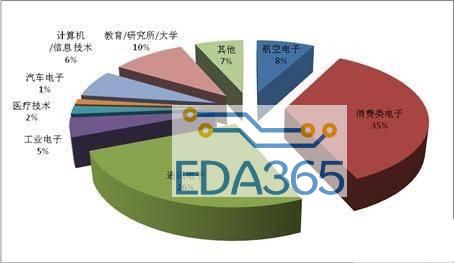

快速原型工具除了令用户具备开发时间上的优势,成本风险方面的减少将令其在中国本土IC设计中的需求显着增加。HAPS-80基于FPGA的原型系统和ProtoCompiler软件现在已可供货。

同时也可直接观看视频,了解更多关于HAPS的强大功能。

热门文章

更多

热门文章

更多