人们通常用每秒百万条指令(MIPS)来衡量微控制器(MCU)的计算性能,但是没有任何两个MCU/SoC架构是完全相同的,加速不同应用性能的集成度也不相同。因此,在采用适当硬件特性的情况下,固件应用可减少对CPU资源的占用。在移植到不同架构的过程中,如果开发人员只关注MIPS,仅以MIPS来预测应用所需的计算性能,那么就会大错特错了。本文将就典型的计算问题分析MCU/SoC的多种架构特性,目的是说明MIPS并不能真正反映器件的计算性能,并探讨我们应当如何应对这一问题。此外,鉴于目前比较此类产品系统级功能的基准标准较少,本文还将专门重点讨论运行速率在100MHz以下的MCU/SoC器件。

100MHz以下架构的特点

100MHz以下的MCU通常使用8位、16位或32位架构,数据总线宽度为8位、16位或32位。这些产品也可分为其它多种类型,如Harvard/Von Neumen和RISC与CISC等,每种类型都有其引人关注的不同之处。对大多数MCU而言,不同的指令需要执行不同的机器资源。此外,振荡器频率通常与机器工作周期不同,比如,就经典的8051而言,振荡器的12个周期才相当于机器工作1个周期。而对许多PIC器件而言,4个振荡器周期就对应于1个机器工作周期。

下面我们通过一个示例来更好地了说明这一问题。假设某器件的振荡器频率为20MHz,其两个振荡器周期对应于1个机器工作周期。此外,指令执行需要1到6个机器工作周期。那么,该器件的MIPS额定值是多少呢?我们将振荡器频率除以2,得到可用的机器工作周期为1千万。不过,如何将机器工作周期转换为MIPS则取决于我们如何看待这一问题。如果您是营销人员,您会只专注于情况,也就是假定每条指令只要一个工作周期,这样这款产品的性能就是10 MIPS。如果您想了解的理论性能,那么就会假定每条指令需要6个工作周期,这就会得到1.66(10/6)MIPS。这里我们得到了和的MIPS。对典型应用而言,实际的MIPS性能介于二者之间,具体取决于应用的指令集组合。我们这里还作了令一个假定,即认为不同的架构指令计算性能类似,但这基本上是不现实的。

我们这里假定机器工作周期数量是决定器件执行指令数量的因素。下面,我们设想一下闪存对处理性能的影响。一般而言,闪存提供数据的速率不超过20MHz。因此,如果CPU运行速率超过20MHz,而用闪存执行指令,那么闪存数据速率就成为了的瓶颈。在此情况下,我们可让闪存总线带宽高于数据总线带宽,并创建指令缓冲器以跟上指令速率,从而解决上述问题。要做到这一点,CPU就要在执行当前指令时调用下一条指令。这种做法对线性代码而言没问题。但不幸的是,实际系统代码很少是线性的。每次代码出现分支,指令缓冲器都必须重构。另一种改进性能的办法是添加缓存容量。简而言之,如果一个MCU/SoC管理闪存的效率较高,而另一个效率较低,则即便机器工作循环和指令集相同,性能数据也将大不相同。

我们已经比较熟悉类似上述的各种因素,开发人员通常会在比较不同器件的性能时考虑到这些相关因素。下面我们来谈谈某些不太明显的因素。

DMA对MIPS的影响

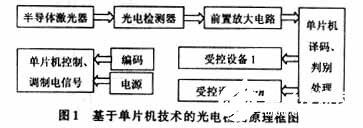

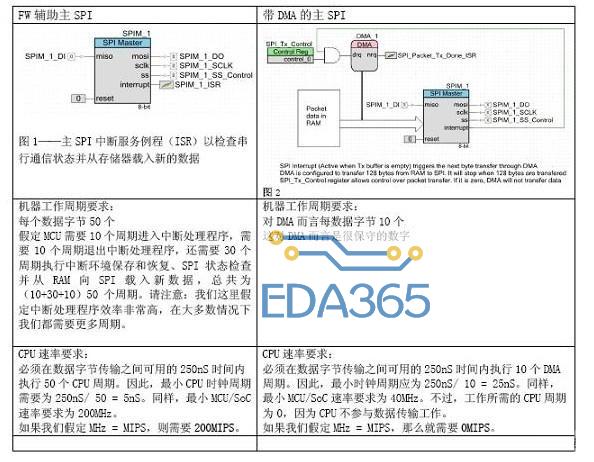

某MCU/SoC器件支持DMA(直接存储器存取)功能,其能将CPU从存储器存取工作中解放出来,从而提高性能。我们怎么*估DMA对MIPS的影响呢?先来看看主模式下串行通信协议SPI的典型使用情况。SPI是一个很好的例子,因为它通常是MCU/SoC上吞吐量的板内通信外设,而且配合存储器、以太网、无线收发器芯片等一同使用。

假定:

SPI速率:8Mbps

数据包大小:128字节

数据吞吐率要求:每个数据包160uS

如SPI速率为8Mbps,那么传输1个字节需要1uS。因此,传输128个字节需要128uS。我们的预算为每个数据包160uS,这就剩下32uS(160-128)用于SPI管理。这32uS的预算要平均分配给128个字节,因为系统每一个uS都要载入一个新数据字节。32uS除以128即可得到SPI管理每数据字节传输有250nS的时间。

就上例而言,DMA将MCU/SoC速率需求降低了160MHz,而将CPU处理能力需求降低了200MHz。如果我们假定周期相当于MIPS,那么本应用的DMA就相当于一个200MIPS处理器。

DMA实现的高效MIPS在很大程度上取决于吞吐量需求。我们再举一个本应用的极端例子。假定每个数据包没有时间限制,那么DMA每字节节约的CPU周期数达50个,那么就128个字节而言,周期数节约可达6400个。如果MCU需要在16MHz的情况下支持8MHz SPI,且128个字节的数据包每秒只传输,那么不支持DMA的MCU/SoC运行速率就需达到每秒16,00*00条指令,性能水平和支持DMA的MCU每秒160万条指令相当。因此,就这一特殊的使用而言,DMA的影响可以忽略不计。

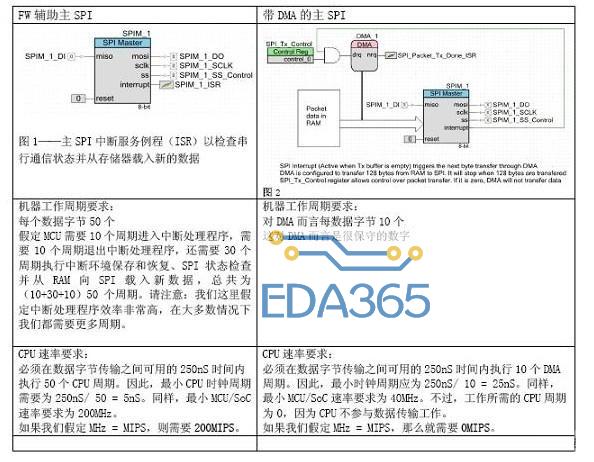

协处理器对MIPS的影响

MCU/SoC带协处理器的情况并不少见。协处理器能并行处理某些高计算强度任务,将CPU解放出来并提高处理器的MIPS效率。

我们不妨设想一下这样一款应用,其输入音频数据进入后由ADC采样,采样频率为44.1Ksps。假设我们希望抑制50或60HZ的直线频率。为此,我们需要使用数字带阻过滤器。

采样速率:44.1Ksps,采样间隔22.7uS

FIR过滤器抽头数:128

为了简化说明,我们不考虑过滤器的输出级。

就上例而言,协处理器将CPU速率要求降低了44.1 MIPS。请注意,该示例采用了简单的FIR过滤器。如果需要更复杂的过滤器,那么MIPS要求可能会高得多(数百MIPS)。

可编程数字器件对MIPS的影响

一些MCU/SoC器件的可编程数字逻辑为CPLD或FPGA逻辑形式,这使开发人员能用硬件实施CPU功能,而CPU功能传统上是用软件实施的。下面我们来看看可编程数字逻辑对MIPS有什么影响。

我们假设三相无电刷DC(BLDC)电动机的转速为30,000rpm。电动机的转动要求脉冲时序。出于简化目的,我们还假定用霍尔感应器来探测电动机转子的位置。三个这样的霍尔感应器用来实现上述目的。每转60度,霍尔感应器输出之一就会发生变化。如果电动机有两个转子极组,那么两个电气循环将对应于机械转动。这就是说,就完整转动而言,霍尔感应器输出会改变12次。霍尔感应器输出导致6个PWM输出变化。各带配套输出的三个PWM用于创建6个PWM输出。下图显示了霍尔感应器输入同PWM输出之间的关系。PWM值为正说明PWM高压侧工作,值为负则说明PWM低压侧工作。

下面我们来分析通常如何实施BLDC转换,以及如果器件具备可编程逻辑(CPLD或FPGA)功能,又将如何简化BLDC转换。

就上例而言,可编程数字技术将CPU速率要求降低了1MIPS。如果电动机转速较低,那么该技术对MIPS的影响也较低,反之亦然。上例采用了优化组装和简单的开环控制。实际应用会更加复杂,且通常使用C代码,以简化维护和再利用。如果使用一般性C代码,则MIPS要求会增加到3 MIPS。几乎所有电动机控制应用都需要类似于PID控制的多控制回路,这提高了计算要求。不过,如果通过硬件来完成相同工作,那么就能确保CPU占用为零。因此,整个电动机控制应用的MIPS需求介于5到10 MIPS之间,而采用硬件方法,需求则为零。

基于可编程逻辑的实施方案具有较高的再利用性,且不存在任何集成问题。实施一个电动机控制所需的可编程数字逻辑要求非常低,因此我们能在硬件中实施多个电动机控制和转换逻辑。如果用CPU完成相同的工作,由于我们无法同时处理两个中断,那么MIPS需求就会增长好几倍。此外,为了保证合理的中断响应时间,CPU运行速率必须比速率要求快得多。因此,我们能用可编程逻辑轻松地实施完整的BLDC电动机控制系统,比如4个这样的系统。不过,如果用MCU固件来实现相同的任务,则需要约100 MIPS的性能。

正如本文所述,MIPS并不能代表MCU/SoC器件解决系统级问题的真正能力。如果器件具备上述所有功能,那么什么样的器件MIPS性能才适用呢?200 MIPS、500 MIPS还是1,000 MIPS?在所有情况下,MIPS不过是一个意义非常有限的数字而已。

那么,开发人员如何确定适合应用需要的器件呢?不幸的是,这个问题并不太容易回答:

·确定应用中存在关键计时或CPU性能要求的区域。

·确定MCU/SoC厂商是否提供应用说明或类似于您所需应用的示例项目。如果已经提供,则能为您针对既定MCU/SoC来优化应用的程度提供指导。如果没有提供,则应想办法找到使用给定架构实施应用的潜在办法,并了解您可使用哪些硬件特性。

·根据上述示例所示粗略估算MIPS性能要求。计算不必特别。您应尽力确定潜在的巨大差距。在上述所有示例中,性能差异都已足够大,计算已非必要。

·如果性能差距较小,比如在10%到20%之间,而工作任务是应用的主要组成部分,则的选择是用厂商的开发工具包创建特定的实施方案,检测实际性能差距。

·如果您计划购买大量器件,则有关要求可作为RFQ(询价单)的一部分。这让厂商能根据您的特定应用提供器件性能相关信息。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多

.jpg)