从TI第一颗DSP诞生至今已有25年,成就了无数辉煌。多核、SoC的发展方向使DSP将继续高速成长,同时,它的发展也正在面临来自FPGA、ASIC的挑战。

DSP概念最早出现在上个世纪60年代,到70年代才由计算机实现部分实时处理,当时主要用于高尖端领域。由于DSP技术与大量运算相关,每秒完成百万条指令运算就变为一个新的单位MIPS(每秒百万条指令)。80年代,有些公司陆续设计出适合于DSP处理技术的处理器,于是DSP开始成为一种高性能处理器的名称。TI在1982年发布了第一颗DSP芯片,名为TMS32010,这是一个处理速度达5个MIPS的处理器。

加入TI公司有12个年头的清华才俊郑小龙,从技术应用工程师打拼到负责DSP在中国的销售业务,熟谙DSP圈里的事。他谈起了DSP诞生的故事:

那时只有两种处理器,一种是作为PC核心的CPU,另一种是微控制器MCU。这两种处理器的在进行大量运算时都面临技术瓶颈,业内就在考虑 “是不是需要一种高速的数字信号处理的器件”。那个时候,数字信号处理的理论已经有了,像滤波器、编码解码等对于乘加结构要求很高,如果用CPU来处理的话,指令非常多、效率比较低;而如果在处理器中就有这样一个乘加结构,数字滤波器就可以实现实时的处理结果。

DSP刚开始出现时,采用了NMOS工艺,然后由于功耗的原因,很快转到CMOS,例如C54、C55等型号中的“C”就表示CMOS。那个时候成本还是比较高的,实现每个MIPS的成本高达10~100美元,成为商品化的障碍。

本文分四个部分:

发展轨迹:DSP历史的三个阶段

DSP演进图:性能、价格、功耗是不变的追求

未来趋势:DSP走向多核与SoC

DSP不惧竞争?当DSP遭遇FPGA、ASIC

发展轨迹:DSP历史的三个阶段

TI首席科学家兼DSP业务开发经理方进 (Gene Frantz)在年前接受电子工程专辑采访时曾这样说过,“DSP产业在约40年的历程中经历了三个阶段:第一阶段,DSP意味着数字信号处理,并作为一个新的理论体系广为流行;随着这个时代的成熟,DSP进入了发展的第二阶段,在这个阶段,DSP代表数字信号处理器,这些DSP器件使我们生活的许多方面都发生了巨大的变化;接下来又催生了第三阶段,这是一个赋能(enablement)的时期,我们将看到DSP理论和DSP架构都被嵌入到SoC类产品中。”

80年代开始了第二个阶段,DSP从概念走向了产品,TMS32010所实现的出色性能和特性备受业界关注。方进先生在一篇文章中提到,新兴的DSP业务同时也承担着巨大的风险,究竟向哪里拓展是生死攸关的问题。当设计师努力使DSP处理器每MIPS成本降到了适合于商用的低于10美元范围时,DSP在军事、工业和商业应用中不断获得成功。到1991年,TI推出价格可与16位微处理器不相上下的DSP芯片,首次实现批量单价低于5美元,但所能提供的性能却是其5至10倍。

到90年代,多家公司跻身DSP领域与TI进行市场竞争。TI首家提供可定制DSP——cDSP,cDSP 基于内核DSP的设计可使DSP具有更高的系统集成度,大加速了产品的上市时间。同时,TI瞄准DSP电子市场上成长速度最快的领域。到90年代中期,这种可编程的DSP器件已广泛应用于数据通信、海量存储、语音处理、汽车电子、消费类音频和视频产品等等,其中最为辉煌的成就是在数字蜂窝电话中的成功。这时, DSP业务也一跃成为TI最大的业务,这个阶段DSP每MIPS的价格已降到10美分到1美元的范围。

21世纪DSP发展进入第三个阶段,市场竞争更加激烈,TI及时调整DSP发展战略全局规划,并以全面的产品规划和完善的解决方案,加之全新的开发理念,深化产业化进程。成就这一进展的前提就是DSP每MIPS价格目标已设定为几个美分或更低。

SP演进图:性能、价格、功耗是不变的追求

无疑,CMOS工艺的改变大大降低了功耗,而且随着工艺节点从3微米、0.8微米、0.1微米以及未来的纳米工艺,低功耗是DSP一个不变的特性。同时,DSP的主频不断得到提升,从开始的5MHz,到100MHz、200MHz。

“一个关键的转折点出现在90年代中期,TI开发出多并行处理结构,1997年推出了C6000 DSP,有8个并行运算单元,原来每个单元性能可达200MPS,这样一下子提高了8倍到1600 MIPS。” 这些运算单元可以有不同的组合,分为2组、每组4个,包括逻辑处理、数字处理、乘法运算、移位处理四类单元,分别适合不同的应用。这一时期,DSP已广泛用于数据通信、海量存储、语音处理、消费音视频产品等,特别是在蜂窝电话领域的成功。郑小龙说道,“今天针对基站应用的C6416主频达到1.1GHz、处理能力超过8000MIPS。”

性能、价格、功耗永远是DSP追求的目标。在这个目标的驱动下,每隔十年DSP的性能、规模、工艺、价格等就会发生一个跃迁。如表1所示,DSP的演进同样遵循着摩尔定律,伴随着集成度的不断提高,是性能的提升、价格的下降。

针对DSP功耗的变动趋势,存在一个Gene定律。从图1可见,1982年每MIPS的功耗为250mW,到1992下降为12.5mW,而到2000年仅为0.1mW,2004年到0.01mW,而预计2010年将挑战0.001mW。Gene定律认为,DSP功耗性能比每隔5年将降低 10倍。

图1:Gene定律及DSP功耗性能比变化

未来趋势:DSP走向多核与SoC

DSP的发展是非常幸运的,几乎以2倍于半导体工业的增长速度在成长。根据行业分析机构Farward Concepts的预计,在未来5年时间里,DSP市场将以12%的年复合增长率增长,该公司总裁Will Strauss认为:“DSP技术在未来几年的发展将远远大于其在问世后25年之内的发展,并将使人类世界变得前所未有的安全、智能化和联网化。”

在多核故事不断上演的今天,DSP同样也在向多核转变,特别是面向高速、高密度数据处理应用。在TI最近公布的无线基础设施的多核DSP中,已经有一款6核方案,在未来25年可能一个DSP芯片将集成百个处理器。

TI公司高级副总裁Mike Hames在TI刚刚举办的开发商大会勾勒出一系列多核应用新的机遇,“人的衣服可以给人发出健康警报,自动交通工具可以彼此通信提醒是否会延期出发,安全系统可以识别朋友和敌人并采取相应对策,而便携式媒体设备则可以让用户远程访问到属于自己的任何电子设备和数据。”

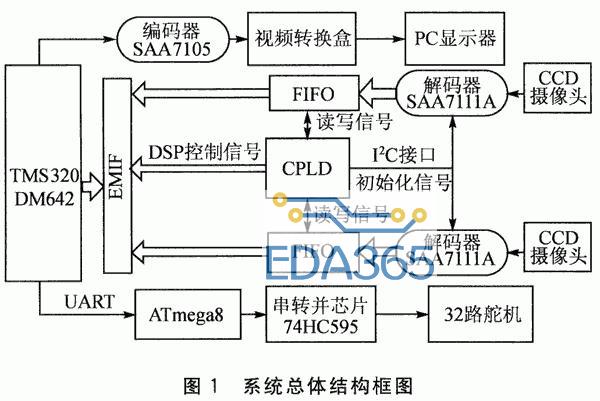

然而对于那些不属于高密度的应用,郑小龙认为,“将来的发展方向是SoC,而不是多核。”达芬奇平台就是一个SoC的典型例子,它采用了DSP(C64x)和ARM(ARM9)双核架构,以及视频前端、视频加速器和很强继承性的软件,专门针对数字视频应用而设计。

方进先生认为,在第三个阶段(赋能时期),SoC集成系统将在系统处理器(如ARM)的控制下,同时使用可编程DSP和可配置DSP加速器,这些新的SoC将成为许多创新性产品的开发平台。可编程SoC (配合适当的可配置)是未来DSP的生存之道。他说,“这听起来像一种限制,但事实上将带来无限的创新机会,例如娱乐、安全和医疗等将是DSP未来三个应用领域。”

DSP不惧竞争?当DSP遭遇FPGA、ASIC

但DSP厂商未来的日子也并不轻松,随着FPGA与ASIC向DSP应用领域的渗透逐渐扩展和加速,竞争在日益加剧。

Altera和赛灵思这两大FPGA冤家,一方面在65nm擂台上不断施展才艺,颇有“道高一尺魔高一丈”的拼劲,比肩共进;同时,也不断将FPGA触角伸向更为广泛的领域,性能和资源的优势自不必说,他们还致力于通过降低功耗和成本等手段,在消费类、嵌入式等领域使FPGA与DSP之间的差别越来越小。

例如,几天前Altera刚刚发布了65nm低功耗(LP)工艺的Cyclone III FPGA,在可编程逻辑发展历史中,它比其他低成本FPGA产品能够支持实现更多应用。其片上资源包括5K至120K逻辑单元(LE),288个数字信号处理乘法器,存储器达到4Mbits。Cyclone III在性能上的提升在于两个方面,一是每逻辑单元成本降低20%,二是比同类FPGA竞争产品的功耗低75%!

据Altera负责广播、汽车电子及消费电子业务的副总裁Tim Colleran称,250多家参加了早期试用计划的客户已经在大量应用中采用Cyclone III FPGA进行设计,比如艾默生的高性能嵌入式电机控制项目、Let It Wave的下一代船舶导航产品的视频处理和显示驱动等。

赛灵思则在其FPGA中引入DSP模块——XtremeDSP技术,提供针对航天和军用产品、数字通信、多媒体、视频和成像行业的高性能定制 DSP 解决方案,目前推出的DSP产品包括新小型化 SDR 开发平台、常见数字无线电系统(CDRSX)开发平台,以及用于BDTI公司的基础研究中,探索FPGA如何满足DSP应用需求、何时使用 FPGA/DSP或是二者的结合。

BDTI一项最新研究结果显示,在多个DSP高端应用中FPGA将扮演越来越重要的角色,例如高端通信基础设施等需要大量并行运算且对性能要求很高的应用,FPGA的性能优势要超过独立DSP;甚至,传统上总是与高成本相联系的FPGA在某些设计应用中比DSP方案还便宜。BDTI也同时指出,FPGA不会在一夜之间彻底颠覆现有格局,在高端通信应用中,将是FPGA与ASSP、ASIC、DSP、通用处理器这些已有系统共存。

除了FPGA巨头,一些初创公司也正在进入DSP的应用领域,以更低成本的解决方案冲击DSP的视频应用。例如从事多媒体处理器研发的北京的希图(C2 Microsystems),专门针对音视频、图象应用开放优化的可编程解决方案,宣称其对手只有达芬奇平台。而另外一家,成立于2005年的北京维柯视(W&W)则是致力于H.264的ASIC研发,提供视频压缩编解码技术和配套产品解决方案。

从郑小龙的谈话中,感到DSP似乎不惧怕这些竞争,低功耗、软件可编程性是DSP独特的优势,SoC的发展也将为DSP赢得更多优势。

FPGA有它不尽如任意的方面。许多DSP设计者可能并不熟悉面向DSP的FPGA,郑小龙称,“使用DSP有很好的继承性,包括软件、操作系统、多媒体框架等都有很强的继承性,有丰富的第三方支持,而通过FPGA硬件进行编程则需要复杂的软件,这就涉及到建立一个生态系统的问题。”

ASIC低成本也伴随着灵活性不够。对于一些新兴标准,需要有一个完善的过程,如果要实现多制式、各种各样的应用,ASIC也将受到各种限制。郑小龙表示,AISC更多是在抢占成熟的或低端市场,比如MP3等,高端产品还是由DSP实现。DSP的未来一定是提供高附加值,就是给厂家做特色产品、创新产品提供一个平台,例如DMA、可视电话、会议电话等,多功能、多制式需要灵活的软件支持。

在DSP目前优势的基础上,降低成本也是未来DSP或SoC平台的努力目标。最早是ADI将Blackfin平台做到10美元以下,后来 10美元也成为TI的一个目标,目前,达芬奇平台已经有低于10美元的解决方案。郑小龙表示,今后达芬奇还将针对具体类别的应用推出性能、成本优化的解决方案。

另外一个重要方面是功耗。以低功耗著称的DSP对降低功耗的追求是无止境的,方进称:“我们需要我们改变对低功耗的思考模式。”他提出了两种不同的低功耗定义:一个是在不牺牲性能的前提下把功耗减至最小,称之为“低功耗”;另一个称为“超低功耗”,则是指牺牲部分性能,务求尽最大限度把功耗减至最小级别。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多