以前我们依靠时钟衡量DSP性能高低,然而这样的对应关系并非线性,而市场的需求却在线性增长,那如何实现性能的提升?

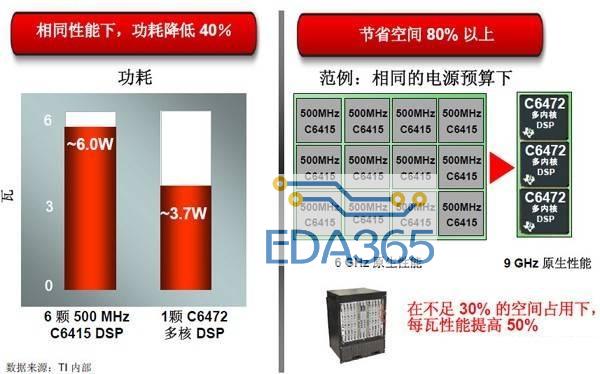

“有两种方式:多核并行处理和DSP阵列,”在2009年11月5日德州仪器6核DSP—— TMS320C6472的发布会上,其通用DSP业务发展经理郑小龙告诉EEWORLD,其中,DSP阵列可以依靠在高性能DSP上增加高速接口实现,但这时却又碰到了另外一个问题:系统功耗和尺寸非常大。聪明的芯片厂家将多个DSP核集成在一起,于是出现了“多核DSP”的概念。

今天推出的这款6核DSP就是其中之一。与此前TI推出的C6474一样,其前缀“TMS320”是TI DSP的标准型号,其后的“64”说明这是高性能系列,而“7”专指多核DSP,“2”则说明其功耗很低,旨在满足要求极低功耗的处理密集型应用的需求。

TI C6472是TI针对电源优化的多核处理器, 在业界总工作频率为 3GHz 的所有多核 DSP 中,C6472 DSP 具有最高的处理性能与最低的功耗,可实现 3.7W 性能与 0.15mW/MIPS 低功耗。TI 该款低功耗 C6472 可用于支持能够驱动多通道、要求最高性能密度以及设计人员需要实现复杂功能的应用领域。此外,采用 C6472 的众多应用都无需任何外部存储器,从而不仅能够进一步改进功率曲线,同时还能大幅降低器件成本。这些器件理想适用于广泛的应用领域,如高端工业应用、测试测量、通信、医疗影像、高端成像及视频,以及刀片服务器等。为了加快在多核器件上优化运行代码的编写进程。

C6472 DSP 的主要特性与优势:

• 6 颗高速 C64X+ DSP 内核,运行频率为 500MHz、625MHz、700MHz,并能够与其他 C64X+ DSP 内核实现全面后向兼容;

• 高达 4.2 GHz/33600 MMAC,4.8MB 片上 L1/L2 RAM;

• 拥有业界最低功耗,0.15 mW/MIPS 时性能达 3GHz;

• 优化的 DSP 架构能够最大限度地提高片上子系统的性能。此类架构的优势之一在于,除了每个内核都具备专用的 L1 和 L2 存储器外,C6472 还具备每数据存储器 768KB 的共享 L2 程序以及共享存储控制器,能够实现高效而灵活的DSP 内核间通信;

• 包含丰富的器件外设,如千兆以太网、串行高速 IO (SRIO)、DDR2、电信串行接口端口 (TSIP)、主机端口接口 (HPI)、Utopia、内置集成电路 (I2C) 总线以及通用输入/输出 (GPIO)。

[page]

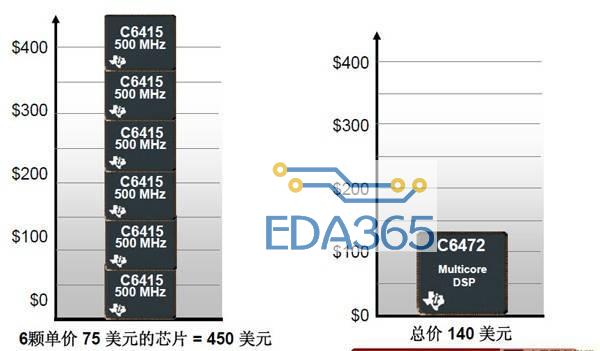

据悉,TMS320C6472 现已开始供货,每千片起价为140美元。同时,为了更便捷、更经济地评估 C6472 器件的性能,TI 还同步推出了一款多核处理器评估板 (EVM) —— TMDXEVM6472,据郑小龙介绍,TI的开发工具分为几百美元的入门套件和上千元的EVM,而此次推出的评估板,是一款极具性价比的评估模块,以入门套件的价钱获得了EVM的服务,此款EVM售价为349美元。

[page]

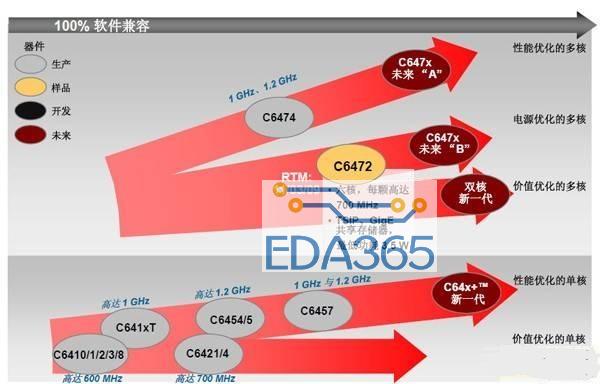

附:德州仪器高性能DSP发展策略

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多