作者:Evan 远远,魔都漂流的孤独患者。热爱电力电子和模拟电路,希望大家一起交流。

在上一期中,有朋友问 12V 哪里来的? 在数据中心场合或者服务器等 48V 和 12V 的母线都是比较常见的。据我熟知的而言,48V 仍然要转换成 12V 的 bus,作为母线电压输入。因此,这是一个比较常见的例子。

被我忽略的一点是,电容的 RMS 电流,流入电容的电流会引起电容温升,有些电容制作商会给出 RMS 电流和温升的关系曲线,更利于计算和选择。比较推荐使用的是 X6S 或者 X7R 这种温度范围较宽的陶瓷电容。

输入电容的 RMS 电流计算公式为

暂时抛出两个计算式以做补充。接下来,就可以搭一个简单的 SIMetrix/SIMPLIS 仿真模型。根据之前几期的介绍,首先需要搭建一个恒定导通定时器,当然,都是基于行为模型,精度仅够学习观摩使用,各位模拟设计的大佬,多多担待。

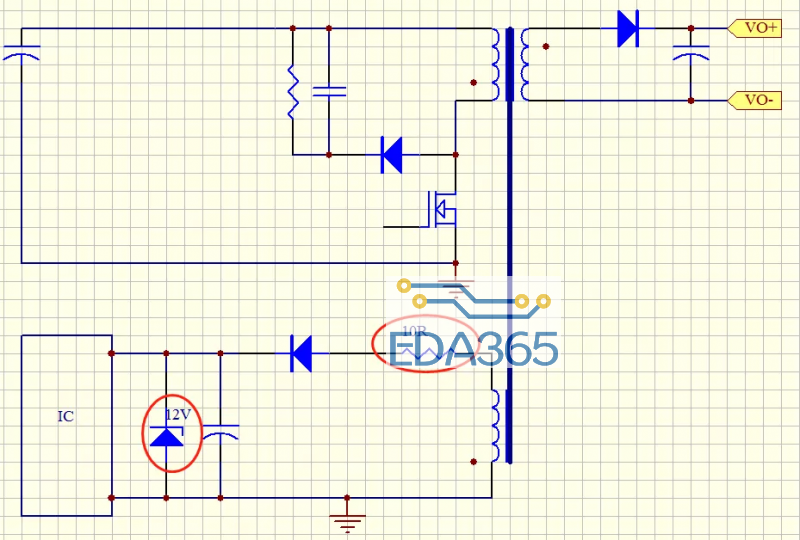

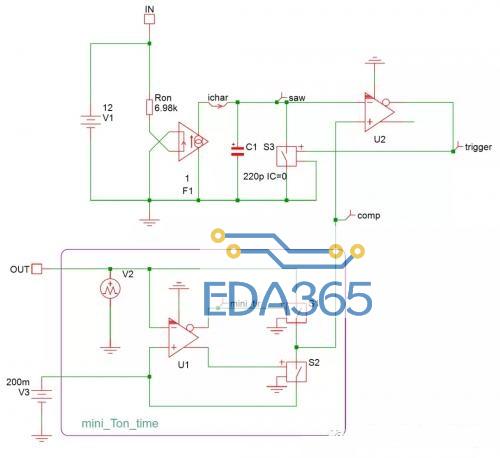

图 27 恒定导通时间定时器

首先,需要获得与 Vin 成正比的电流源,可以使用压控流源直接转换成电容充电电流 ichar,也可以使用如图所示的流控流源,它将输入电压 /Ron 的电流转换成电容充电电流 ichar。后者这种情况更接近于实际底层的设计,因此姑且采用这种形式。ichar 是一个与 Vin 成正比的可控恒流源,电容电压将会线性上升,被送入比较器的负端。比较器的正端接了一个模拟启动过程的电路,当系统刚启动时,输出电压为 0,此时将电容电压 vsaw 无法与输出电压比较,比较器完全失去功效。在输出电压建立之前,使用一个 200mV 的内部基准做为比较器的正端输入,这也对应着 Ton 的最小导通时间;当输出电压大于 200mV 时,再切换至输出电压做为比较器的正端输入,就可以完成 Ton 与输出电压成正比的要求。

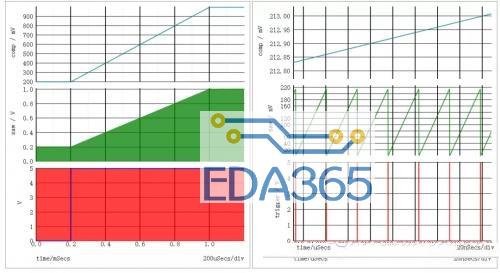

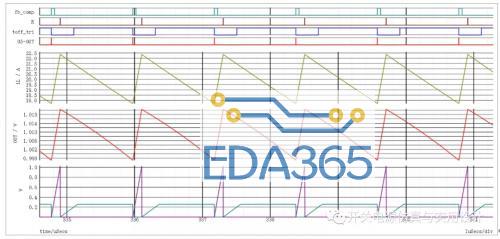

图 29 COT 定时器的模拟波形

S3 是一个理想的 Switch,用来对电容电压放电,从而形成锯齿波的下降沿,它的触发信号在 COT 控制模式中是由驱动脉冲结束的信号控制,此处仅作定时器的验证,使用比较器的反向输出信号做为触发信号。电压源 V2 设置成一个从 0 开始的 ramp 信号,升到 1V 时保持。用于模拟输出电压软启动的过程。

从仿真波形上看,完全和设想的一致,比较器的正端在先由 200mV 开始,达到比较器触发点时,斜坡上升,最后保持在 1V。相应的,Ton 定时器的锯齿波信号的幅值跟随变化,由于比较器的斜率固定,Ton 的时间一直会也会跟随变化。

Ton 时间可以计算为

调整电容 C1 和 Ron 就可以获得需要的 Ton 值,按照图的参数计算 Ton=128ns,Ton_min=26ns。

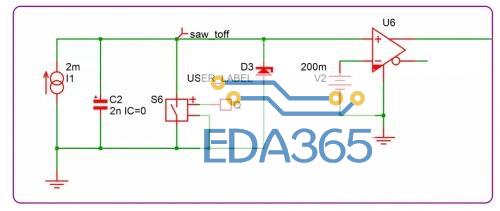

图 30 COTToff min 定时器

同样地,最小关断时间的定时器可以如法炮制,此时可以使用一个简单的恒流源给电容充电,需要注意的是,当 Toff_min 时间结束的时候,电容 C2 的正端电压 vsaw_toff 会大于 200mV,比较器输出电平为高,而这个高信号需要一直保持住,直到下一个 Ton 的脉冲上升沿到来,才对电容进行放电,以释放这个状态。而电容电压又不可一直充电,否则充电电压会很高,所以使用一个钳位稳压管使得稳压值略大于 200mV 即可。

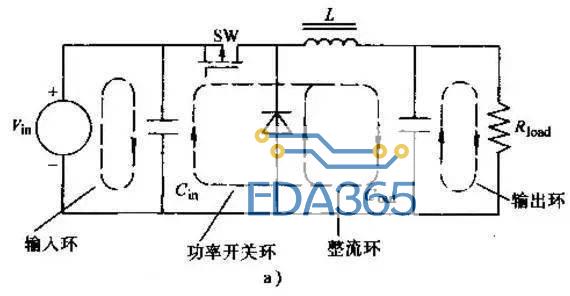

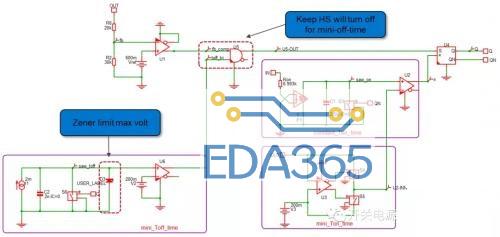

图 31 基本的 COT 控制模式的框图

我们来说下它的具体的控制逻辑,设定的输出电容的 ESR 较大于临界值。

利用分压电阻采样输出电压,获得反馈电压 vfb 信号,与基准电压 600mV 比较,当 vfb 低于 600mV 时,比较器 U1 输出高电平,而此时的 Toff_min 定时器的输出跟上述的那样保持高电平的状态。

那么与门 U5 的两个输入全为高电平,其输出信号 U5-OUT 为高电平。这个信号输入 RS latch 的 S 端,置位 Q 信号,Q 此时拉高,若忽略死区时间,Q 即作为上管的原始驱动信号,QN 则为下管的原始驱动信号。此时上管开通,电感电流线性上升,对应的输出电压的 ESR 纹波也会线性上升,反馈电压 vfb 的纹波电压也在线性上升。

此时,Q 拉高还会开通 switchS6,将 Toff_min 定时器电容上的电压放电,也即将 Toff_min 定时器的输出拉低,也即是将 U5-OUT 信号拉低,这保证了 RS latch 的逻辑不会同时出现高的情况,其 S 上只会出现一个短暂脉冲。

图 32 COT 控制模式基本逻辑和主要波形

此时,Q 拉高,意味着 QN 拉低,QN 拉低断开了 switch S3,此时 Ton 定时器就开始从 0 开始充电,当电容 C1 的电压大于 Vout(或者 200mV 的基准电压),比较器 U2 的输出发生翻转拉高,此时 RS latch 的 R 端为高电平,S 端为低电平,输出信号 Q 拉低,结束 Ton 时间的驱动脉冲信号,QN 则拉高,使得 switch S3 闭合,Ton 定时器电容 C1 放电到 0,比较器 U2 的输出再次翻转拉低。因此,也保证了 RS latch 的逻辑,其 R 上只会出现一个短暂脉冲。

当 Q 拉低时,同时关断了 switchS6,启动了 Toff_min 定时器。Toff 定时器电容 C6 电压一直上升,超过 200mV 时,比较器 U6 会一直拉高,直到下一个开关周期来临。

讲到这里,基本的逻辑思路已经很清晰了。但是有一个疑问,怎么保证 Toff_min 的确可以在瞬态响应中完成了关断上管 Toff_min 时间呢?当负载电流增加时,输出电压会产生 undershoot,此时反馈电压 vfb 会持续小于基准电压 600mV,可能会保持几个周期。也就说,比较器 U1 的输出会一直拉高,保持几个周期。当系统开通第一个 Ton 时间后,Q 信号启动 Toff_min 定时器,当比较器 U6 拉高时,与门 U5 的两个输入信号全为高电平,又启动了下一个 Ton 时间。因而,可以证明,在 vfb 一直小于基准电压时,上管的确可以完成 Toff_min 时间的关断。

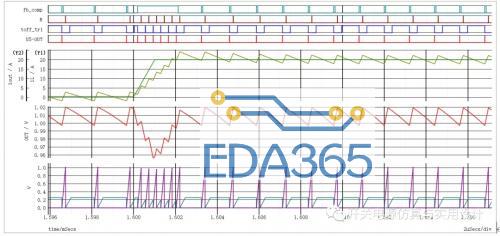

图 33 undershoot 瞬态下 Toff_min 的验证

根据上述的逻辑,跑一次 undershoot 的瞬态,可以看出底部浅绿色 Toff_min 的波形,在动态时刻仅以三角波形式出现,而在其他时刻以梯形波出现。因此的确,如上述逻辑所述那样。

顺便提一点,仿真模型仅仅是为了提高一个更直观的理解,加深对系统思想的理解,也作为个人逻辑思想的验证工具,千万不要为了仿真而仿真。如果你想获得和实际中一毛一样的仿真模型,那需要深入到更底层的半导体物理和 CMOS 模拟电路设计领域,还要考虑杂散参数等问题。这对于 Simplis 工具来说是不适用的,也偏离了建立 Simplis 模型的初衷。

这种仿真模型对模拟 IC 设计者而言,就像一个已经不适合成年人玩耍的儿童玩具,显得有些拙劣。如果能为系统设计者或者电源应用设计者提供一些微小的帮助,笔者已经颇感欣慰了。

APP下载

APP下载 登录

登录

热门文章

热门文章