数字电子产品在性能和电源要求方面已经走过了很长的一段旅程。最初的 8086 处理器具有 10MHz 最大时钟速度,采用 3µm 的半导体工艺,其内核和 I/O 功能采用 5V 电压,功耗仅为 1.8W,这种“单平面”电源设计在其使用寿命内逐渐降低至 3.3V。为了最大程度地减少笔记本电脑和移动设备的功耗,业界逐渐采用了双平面配置,使内核可以在较低的电压下运行,而 I/O 则保持在 3.3V。对于采用 4GHz 时钟和 7nm 半导体工艺的当代处理器,其内核电压已经不到 1V,而峰值功率则高达约 140W。

虽然降低电压可以最大程度地降低功耗,但同时也会降低器件的运行速度。器件绝缘层厚度通常仅为 0.5nm 或大约为两个原子的尺寸,较高的电压会给 CPU 晶体管中的金属氧化物绝缘层施加更大的应力,并由于“隧道效应”的影响而增大漏电和功率损耗。为了达到所需的不断提高的性能,但又要在低电源电压下工作,运行多线程代码的多核 CPU 并行处理已成为一种规范,但这会增大总功耗和电流消耗。

集中式电源系统适合于单平面布置,在低电流下,连接路径上的低压降可保持 IC 的高精度。随着电压下降,电流增大,精度指标也越来越严格。需要使用“中间总线”布置来使系统在较低电流下,电压达到较高的水平,通常为 12V,然后 DC-DC 转换器将电压降至接近负载的工作水平。

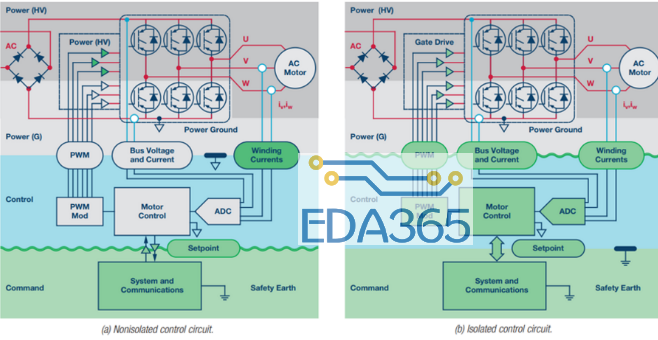

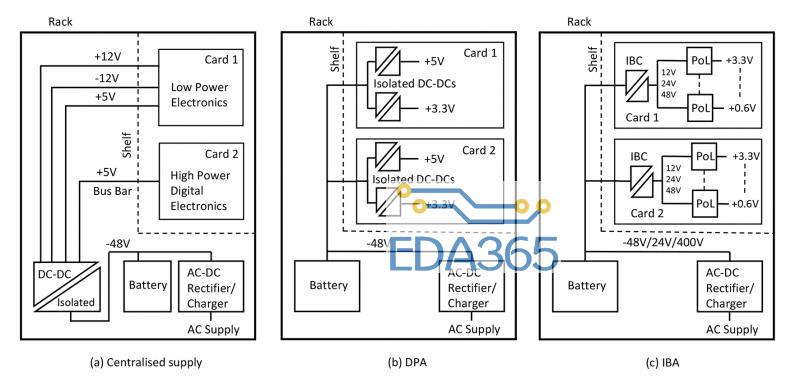

在电信环境中,电源必须可靠,并需尽量减少投资和环境成本。随着计算技术的发展,迫使电源架构也发生了重大变化。在上世纪 90 年代初期之前,集中式电源系统是标准配置,采用一个 AC-DC 整流器产生带有后备电源的 -48V 总线(图 1a)。之后,DC-DC 转换器能够向机柜中的机架提供较低电压,通常为 5V 和±12V。无论是静态还是动态稳压都很差,单个组件故障可能会使整个系统宕机。因此,业界设计了一种分布式电源架构(DPA),将提供后备电池的 -48V 连接至每个机架,在板卡上的隔离式 DC-DC 转换器提供端电压(图 1b)。冗余式板卡现在可以热插拔,从而在负载进行严格电压调节的情况下使系统能够继续运行。许多隔离式 DC-DC 转换器会导致较高的成本,因此有时会使用集中式和分布式的混合配置。

图 1:电源架构的演变。

下一个增强型功能是中间总线体系结构(IBA)(图 1c),其中,每块卡上的单个“总线”(IBC)转换器提供隔离,并将电压降压转换为典型的 5V 或 12V 中间电压,低成本、非隔离式 DC-DC 或负载点(PoL)转换器可提供端电压。总线转换器由 -48V、24V 甚至 400V 供电,以保持较低的初级电流和传导损耗。由于 PoL 转换器通常为宽输入,且不需要严格稳压的电源,根据具体应用,该转换器可以是完全稳压、半稳压或非稳压式。

现代电源架构

IBA 如今在业界已经很常见,在总线转换器有各种变体,以便能够在不同的具体应用中提供最佳整体效率。随着负载不可避免地增大,12V 中间总线电压所涉及的高电流会导致出现一些问题,因此,最新的设计趋向于将总线电压提高至 48V,并规定 PoL 转换器会在极端情况下将该电压直接降至 1V 以下。高转换率会在转换器中产生短脉冲和高峰值电流,由于效率方面的考虑,几年前这些还不切实际。但是,随着半导体和功率转换拓扑架构的发展,这种方法现在被认为切实可行,尤其是考虑到更少的总线电阻性损耗,更小的尺寸和更低成本等竞争优势。出于效率的考虑,可以使用级联负载点。例如,I/O 需要从 48V 降至 3.3V,为另一个负载点供电需要从 3.3V 降至 1.8V。系统设计人员将生成一个“功率树”来表示所提出的体系结构。图 2 所示为 Xilinx SoC 的典型“功率树”。

图 2:Xilinx SoC 器件的典型“功率树”。

PoL 规格

用于 IBA 的负载点必须满足有关输出噪声、电压容差以及静态和动态稳压的严格规范。典型的要求是对于最敏感的负载,例如对于以 1V 运行内核电源,且负载步长为 5A 或更高的 DSP,在所有条件下将输出保持在±3%以内。转换器控制环路必须足够快速,这意味着需要较高的开关频率,反过来又要求使用高性能半导体器件,或者使用最新的宽带隙器件以获得最佳效率。特定负载点应该能够与其他负载点进行“排序”,以便电源轨按正确的顺序升高和降低。CPU 需要与负载点保持通信以动态调整输出电压,并通常通过 I2C 接口使用 PMBusTM 命令监控性能,如输出电流、温度和故障标志等。最新的负载点设计还将具有数字环路控制功能,可针对不同的应用,或随时间而变化的条件导致负载和输出电容的变化,来实现最佳性能。因此,负载点中的控制和监控非常复杂。即使是经典“降压”转换器的基本拓扑,也会通过同步整流和多相操作而得到性能增强,以便在高负载电流下实现所期望的效率,同时保持轻负载条件下损耗较低。

PoL 转换器的规格随负载而有所不同,CPU、FPGA、ASIC、SoC 和 ACAP 器件都有其特殊的需求。在每一种情况下,转换器都必须安装在尽可能靠近负载的位置,以实现最佳性能,从而在电路板布局中出现需要解决如何容纳一系列地址和 I/O 线的问题。因此,PoL 需要非常小巧紧凑,由分立组件构建的 PoL 几乎不可行,而模块式设计则是比较自然的选择。这种方法还具有其它优势,可以使用经过预先测试和认证,并符合行业标准大小的的零部件,以便更充分低利用垂直空间。PoL 中必需的技术还要求在功率级中精心布置电路板中的电源平面、屏蔽层和紧凑的电流环路,以降低 EMI 的影响。相对于主板而言,这些功能在专用型模块的基板(substrate)上更容易实现。对于包含 100 多个组件的典型 PoL,与采用分立解决方案相比,选用模块方案对于库存和采购也明显更加简单。

如果功率级可以作为模块购买,并与第三方电源管理和控制 IC 兼容,也可以采用混合解决方案。在这种情况下,IC 放置在主板,模块则放置在 IC 之上,或有时放置在主板对面。

PoL 格式–替代方案

PoL 转换器具有通孔或可插拔的 SIP 格式,能够占用最少的电路板空间,德州仪器(TI)、RECOM、CUI、TRACO、村田制作所(Murata)、ABB、XP Power、Advanced Energy 以及其他厂商都可提供类似产品。表面安装模块是实现制造经济性的首选要素,这里有多种选择,包括鸥翼式(ull-wing)、块形支脚(block feet)、LGA 和 iLGA(可检查地网格阵列)。输出电压可低至几分之一伏,电流可达 40A 以上。

图 3:各种不同的 PoL 格式示例:TI TPSM 系列(左),CUI V78E 系列(中),村田 MYMG 系列(右)。

例如,Murata 的 MYMGA ‘monoblock’ 系列可通过尺寸仅为 10.5 x 9.0 x 5.6mm 的 LGA 封装装提供 12A 电流,这些器件的输入范围为 4.5~8V 或 8~15V,输出可在 0.7~1.8V 范围内调整,效率峰值则为 93.5%。该系列可满足 FPGA/CPU 对准确电压轨的要求,可提供±1%的最大负载调节率(见图 4)。

图 4:Murata MYMGA 系列可提供±1%的负载调节率。(来源:Murata)

德州仪器(TI)通孔格式的 PoL 转换器 PTH08T250W 可提供±1.5%的严格负载调节率,但却具有 0~50A 的输出负载范围,可以选择模块并联以提供更高的电流。该器件的输入范围为 4.5~14V,输出可在 0.7V~3.6V 之间调节,效率高达 96%。村田制作所和德州仪器的器件均适合 IBA 布置,其中总线电压也得到宽松调节,从而提高了整体效率。

所有转换器都具有全面的保护功能,有些转换器符合分布式电源开放标准联盟(DOSA)定义的通用性能和引脚输出标准。需要注意的一项功能是启动预偏置负载的能力,这种负载可能出现在具有多个电压轨的系统中。更复杂的 PoL 转换器包括更多的监视和控制功能,例如 ABB 公司的‘Lynx’ 系列 中的 Tunable LoopTM 功能,允许用户调节电压控制环路,以最大程度地提高动态性能,同时尽量减小任何特定负载下的输出电容。

模块化 PoL 供应商提供的演示板通常具有图形用户界面(GUI),可以设置回路响应,并能够控制和监视各个参数。

结论

当代处理器和可编程器件都具有非常出色的性能,如今已经广泛应用在从信息娱乐到电信和工业等各个领域。为这些器件提供电源给 DC-DC 转换器设计人员带来了巨大挑战,需要提供越来越低的电压和更高的电流。模块化 PoL 转换器可与总线架构相匹配,能够提供清洁、高性能、高转换效率的电压轨,从而可以明确地解决上述问题。与分立组件相比,所有这些都能够提供一种经济的解决方案。内置智能特性可根据负载要求调整 PoL 性能,并能够添加控制命令和状态信号,从而进一步为应用带来更多的价值。

APP下载

APP下载 登录

登录

热门文章

热门文章