电子产品在CE认证中,经常需要过辐射干扰(<1GHz)测试,常遇到某个频点上辐射(dBuV/m)超标,或者余量不足的情况:

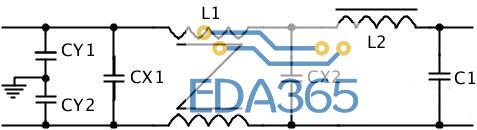

1.如果是低频超标,一般是输入电源辐射出来的,确保使用的DC适配器合格,再进行PCBA板的电源输入处理,通常是线上串磁珠,电容到地等处理。

2.如果是高频超标,一般是某个时钟(系统时钟,晶振时钟,外围芯片时钟脚)的倍频辐射,先确定是哪个芯片泄露,再看此芯片是否存在有引脚直接引飞线出来(扫灯引脚、ADkey引脚等),如果有,要预留磁珠,电容。也有可能是供电电源线辐射出来,也要做相应处理。

3.如果是有一段高峰超标,即可能是某些时钟可变的芯片辐射出来的(SD卡时钟脚),首先确认SD卡外壳正确接地,电源处理,再进行时钟脚和数据脚的处理(一般不建议强推操作)。

对于静电测试,先确认需要接触式打多少V(一般4kV,巴西6kV),空气打多少V(一般8kV)。

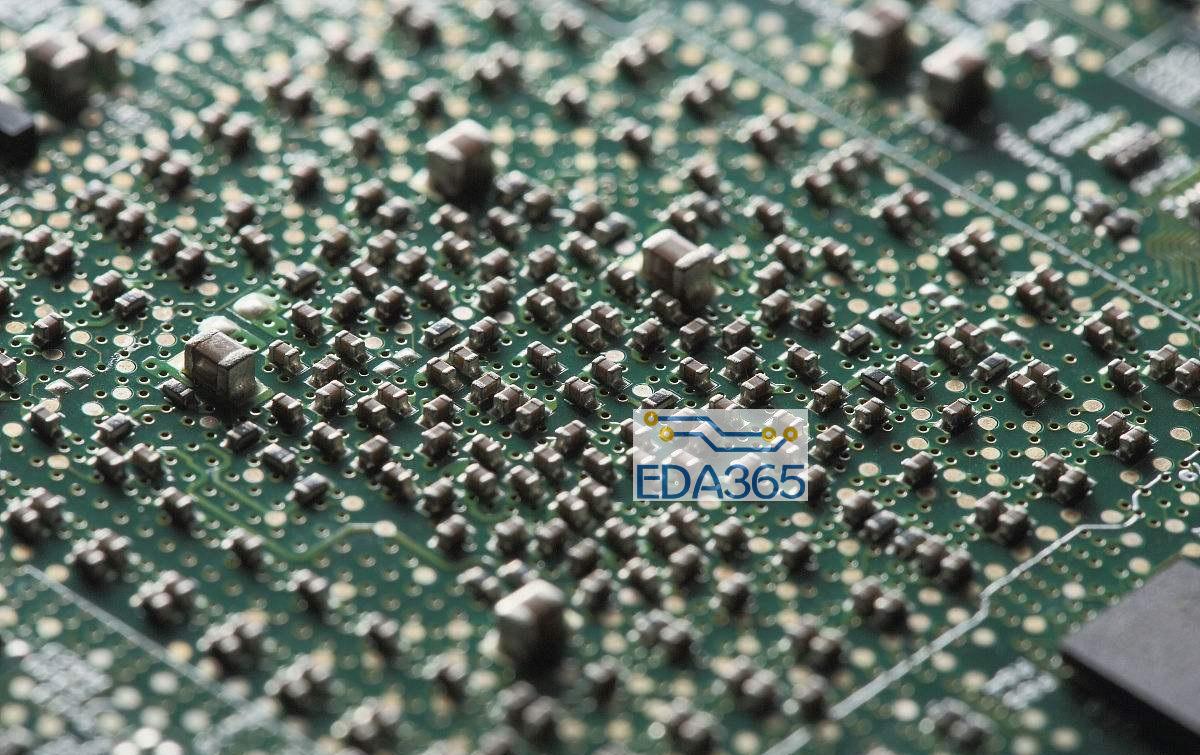

1.PCB要预留有ESD元件焊盘,所有留孔,与外界通信的端口都要进行相应处理。

2.PCB布局和布线,要铺铜处理好,让静电安全顺畅回地。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多