1引言

近年来,随着计算机微处理器的输入电压要求越来越低,低压大电流DC-DC变换器的研究得到了许多研究者的重视,各种拓扑结构层出不穷,同步整流技术、多重多相技术、磁集成技术等也都应用于这个领域。笔者提出了一种交错并联的低压大电流DC-DC变换器,它的一次侧采用对称半桥结构,而二次侧采用倍流整流结构。采用这种结构可以极大地减小滤波电容上的电流纹波,从而极大地减小了滤波电感的大小与整个DC-DC变换器的尺寸。这种变换器运行于48V的输入电压和100kHz的开关频率的环境。

2倍流整流的低压大电流DC-DC变换器的结构分析

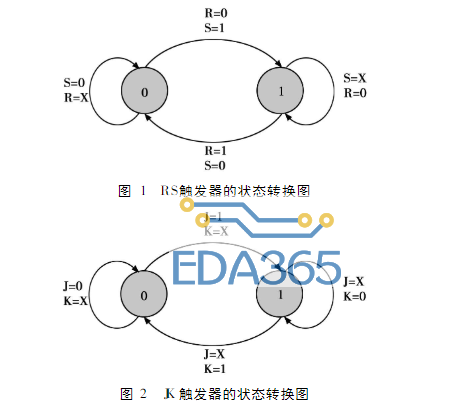

倍流整流低压大电流DC-DC变换器的电路原理图如图1所示,一次侧采用对称半桥结构,二次侧采用倍流整流结构,在S1导通时SR1必须截止,L1充电;在S2导通时SR2必须截止,L2充电,这样滤波电感电流就会在滤波电容上移项叠加。图2给出了开关控制策略。

图1倍流整流的低压大电流DC-DC变换器的电路原理图

图2开关的控制策略

通过以上分析可以看出,倍流整流结构的二次侧2个滤波电感电流在滤波电容上相互叠加,从而使得输出电流纹波变得相当小。

结构中的同步整流器均按外加信号驱动处理,使控制变得很复杂,但在这种半桥-倍流拓扑结构中使用简单的自驱动方式很困难,因为,在这种结构中,如果直接从电路中取合适的点作为同步整流器的驱动信号,在死区时间内当这个驱动信号为零时,同步整流器就会截止。为了在半桥-倍流拓扑结构中使用自驱动方式,就必须使用到辅助绕组。

以单个半桥-倍流拓扑结构为例,见图3,VSEC为变压器的二次侧电压,Vgs为由辅助绕组获得的同步整流器的驱动电压,可以看出即使在死区的时间内,同步整流器的驱动电压也不可能为零,保证了自驱动方式在这种拓扑结构中的应用。

图3自驱动同步整流器电路及波形图

另外,由于在大电流的情况下MOSFET导通压降将增大,从而产生较大的导通损耗,为此应采用多个MOSFET并联方法来减小损耗。

3交错并联低压大电流DC-DC变换器

3.1电路原理图

综上所述,倍流整流低压大电流DC-DC变换器具有很好的性能,在此基础上引入交错并联技术,构成一种新的结构,称为并联低压大电流DC-DC变换器,可以进一步减小输出电流纹波。

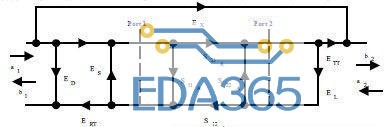

图4为交错并联低压大电流DC-DC变换器的电路原理图(以最简单的2个倍流整流交错并联为例)。

图4交错并联低压大电流DC-DC变换器的电路原理图

3.2变换器的开关控制策略

交错并联低压大电流DC-DC变换器的开关控制策略见图5。

图5交错并联低压大电流DC-DC变换器的开关控制策略

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多