刚入手了SONY Xperia Z5 Premium,其CPU采用了争(fa)议(re)较大的骁龙(Snapdragon )810,那就借此机会谈谈关于桌面CPU和移动CPU的一些东西吧。从小就比较喜欢数码比较多,买了很多这方面的书和杂志,但是对于绝大多数数码设备的核心CPU详细的一些技术参数也只是浅尝辄止未尝深究。上大学以后,关注数码动态不多了,反而更加想去了解之前不怎么探究的微观参数了。好吧,我也不是科班出身,只是凭着爱好不断地追寻和了解,所以下文只是个人的一些看法与总结,多多交流多多批评!

忽然觉得自己这点知识储备居然要论述这么大的一个问题,还是有点头痛啊。我们电力系统分析老师在课上有句话我感觉说的特别好,「你要给别人一滴水,首先你要有一桶水」。那么在下面我主要是以学习笔记的形式来展现吧,希望能和大家共同探讨,共同提高!发现错误请一定要指出!

一 CPU的架构

1.1什么是CPU的架构(Microarchitecture)?

1.1.1 微架构

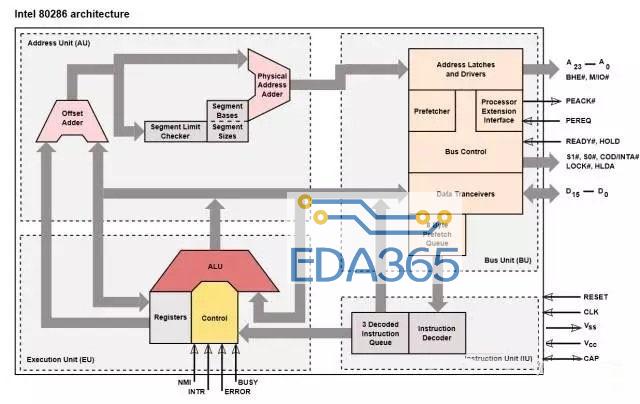

80286的架构

CPU的设计是一个系统工程,通常可以分为微结构(学术界喜欢把micro-architecture翻译成“微结构”,传媒上多见“微架构”)、电路,器件,工艺这几大层面,每个层面内部都有很多细分方向,每个方向都有专家去研究,都有专门的工程团队在做。看一下Wikipedia对微架构的定义

在今日,管线资料路径是微架构中最常被使用的资料路径。这种作法也被普遍的用于微处理器,微控制器,以及数位讯号处理器。管线化的结构允许多个指令在同一时间执行,不同的指令在微架构不同的位置执行。管线分有好几个不同的阶段(stage),这些阶段是微架构的基础。这些阶段包含撷取指令,指令解码,执行指令,以及将资料写回。一些结构还包含其他阶段,像是对记忆体做存取的动作。管线是微架构其中一项主要的工作。执行单元也是微架构的基本元件。执行单元包含算术逻辑单元(ALU),浮点运算器(FPU),load/store单元,分支预测,以及SIMD。这些单元在处理器内进行计算。执行单元的数量,他们的latency(记忆体存取资料的时间)及throughput(将资料存到或是读取出记忆体的速度)影响微架构的效能。

有点不知所以对吧,那就用相对通俗的语言来介绍一下:CPU的架构就是指「接受和处理信号的方式」,也就是说,CPU就是一个工厂,不断的接受到信号,并且处理(运算)这些信号,架构就是在工厂里如何布置那些机器,让机器快速的能够进行以上的那些工序。

CPU的基本组成单元即为核心(core),而核心的实现方式即被称为微架构。微架构的设计影响核心可以达到的最高频率、核心在一定频率下能执行的运算量、一定工艺水平下核心的能耗水平等等。

1.1.2 微架构的发展历程

推动计算机性能提升的一个车轮是半导体的微型化,另一个车轮就是微架构的改进,使得单位时间内可执行的指令更多。

1.1.2.1 微架构的发展之路

微架构的发展历史就是缩短程序运行时间的奋斗史。下面我们来走马观花的看看现代处理器是用的这些主要技术的发展史。

流水线处理

运算器高速化

RISC和CISC

超标量执行

乱序执行

分之预测

缓存

多核

「流水线处理」就是用流水线方式执行指令,以提高指令的处理速度。计算机是进行计算的机器,拥有各种运算的单元,让这些运算能告诉执行非常重要。

x86等CISC(Complex Instruction Set Computer,复杂指令计算机)处理器的指令很复杂,很难采用流水线处理。而RISC(Reduced Instruction Set Computer,精简指令集计算机)是容易进行流水线处理的简单指令架构,以在小型硬件上高速运行为目标。可以认为,RISC是为了实现比CISC更优秀的微架构而重新设计的指令架构。

将流水线处理进一步发展,设置多条流水线,并行处理多条指令,这就是「超标量执行」。但是,如果吓一跳指令会用到当前指令的计算结果,这两条结果就无法并行执行。因此,要改变程序中的指令顺序,先执行能执行的指令,从而提高处理速度,这就是「乱序执行」。此外,遇到条件分支时,尽管不知道接下来要执行哪条指令,但可以进行预测,以提高执行速度,这就是「分支预测」。

半导体的微型化(下一篇会介绍到)带来了处理器的高速化,但是DRAM内存的主要开发经历放在了如何增大内存容量上,速度提高比较缓慢。因此,处理器访问内存就要花费很长时间,导致整体性能无法提高。而在处理器中设置小容量、高速度的存储器,就能解决内存访问时间过场的问题,这就是「高速缓存」技术。

像这样,人们实现了众多处理器高速化技术,但实现这些机制需要大量的晶体管,耗电量也相应增大。为此,与其在每个处理器中嵌入越来越多的晶体管提升性能,还不如制作多个适当大小的处理器,这样同样的耗电量能够获得更高的性能,这就是这几年来流行的「多核心」技术。

1.1.2.2 指令架构

指令架构规定了处理器执行指令的方式及执行结果的样子等「处理器的行为」。指令架构只规定了处理器执行什么指令、执行结果如何,但没有规定处理器内部的实现方式。相对于指令架构的,具体的内部硬件结构就是我们上面说的微架构啦。

在程序运行方面,相同指令架构下可以运行相同的软件,而不同的微架构表现的性能会不同。

最早的电子计算机的速度大大超过机械式计算机,但是人们注意到,计算变快、处理时间缩短之后,人们在更换程序或键盘输入时,计算机就无所事事了,十分浪费。因此,人们把程序像数据那样加载到内存中运行。进一步,为了让同一程序能在其他计算机上运行,人们设计了虚拟内存,能让需要大量内存的程序的运行不受物理内存容量限制;确立了程序和硬件之间的接口——指令架构。

所以说,生产CPU的厂家不断的优化微架构,想不断的提高运行的效率,也就是说指令容易快速地在管线内被撷取,解码与执行,由于指令频繁的被使用,快取便被频繁的使用,这样就使记忆体存取的时间降低。当然,架构的升级不一定就是完全是好的,比如今年高通公司采用了ARM公司的big.LITTLE架构,并且用在了其拳头产品骁龙810上,可是……

我们知道,在最新一级旗舰产品骁龙820已经放弃了 ARM 的官方架构,转而去重新自主设计架构。(坑爹的big.LITTLE)

不过在桌面端,Intel公司有一个著名的战略叫做Tick-Tock,也就是分别在奇数年和偶数年来更新架构和工艺(制程),自从实行这个战略以后,把老对手AMD甩出好几条街,AMD也在自暴自弃,在农企的路上越走越远……

骁龙 820 集成新型 64 位定架构制 Kryo 。借助完全定制自主设计的 CPU,我们能够更好地实施并优化异构计算架构 —— Qualcomm 中国

如果挑选一款CPU的话,一定要看看他的架构,一般来说,架构越新相对来说是越好!

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多