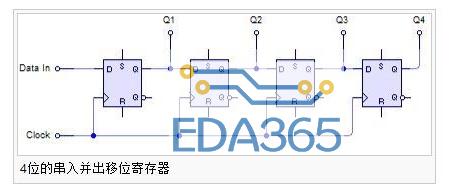

在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

移位寄存器的输入、输出都可以是并行或串行的。它们经常被配置成串入并出(serial-in, parallel-out, SIPO)的形式或并入串出(parallel-in, serial-out, PISO),这样就可以实现并行数据和串行数据的转换。当然,也有输入、输出同时为串行或并行的情况。此外,还有一些移位寄存器为双向的,也就是说它允许数据来回传输,输入端同时可以作为输出端,输出端同时也可以作为输入端。如果把移位寄存器的串行输入端,和并行输出端的最后一位连接起来,还可以构成循环移位寄存器(circular shift register),用来实现循环计数功能。

串入并出

串入并出形式的移位寄存器接法,可以将输入的串行数据以并行格式输出。串行通信要求的几位数据完成输入之后,就可以在输出端的各位同时读出并行数据。

并入串出

并入串出形式的移位寄存器接法,通过下图所示D1-D4并行输入段接收4位外部并行数据,而Q为串行输出的引脚。为了将数据写入到寄存器中,写/移位控制线必须保持低电平。写入完成,需要移位时,写/移位控制线则必须处于高电平,而且必须给予时间脉冲,每提供一个时间脉冲,向左(或向右)移动一位。

串入并出移位寄存器开发经验

对于串入并出移位寄存器以下是我个人的理解和实际开发工程中得出的经验:

由我上图所画,可以得出,一个8位串入数据输入, 8位并行输出。可以看出先移的是高位,就是第一个位进去的到最后会在最高位。

移位寄存器串入并出与并入串出

上图为时序图,A、B是输入。

clean是清0端,低电平有效。就是如果给个低电平那么输出都为0,强制都输出0。一般接高电平。

clock是时钟,上升沿有效。

由上图可以得出如果A、B有一个为低电平,那么阻止新数据的进入,并在下一个时钟上升沿时,将QA端清0。

如果A、B端都为高电平则会使能信号输入,并在下一个时钟脉冲的上升沿之前使输出端QA 置1。每一个时钟脉冲上升沿到来时,输出端的数据会移动一个位,既QA的数据会移动到QB,一直到QH。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多