FIFO移位寄存器的操作原理

下面以长度为8的FIFO移位寄存器为例来说明其操作原理。如图1所示,两边的箭头表示数据移动的方向。A,B,C,D表示被处理的数据,1,2..8表示FIFO移位寄存器中的存储单元。在每一个时钟上升沿到来时,数据向右移动一个存储单元。这样在时钟的控制下,数据从左至右通过存储单元。

使用RAM实现FIFO移位寄存器的处理过程

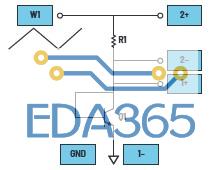

为了达到与FIFO移位寄存器处理的同样结果,以便于数据和操作时钟的管理,使用的RAM存储单元的长度等于FIFO移位寄存器中存储单元的长度加1。读地址比写地址超前一个指针数,即在第n个时钟到来时向RAM中的第k-1个单元写数据,同时从第k个单元读数据。在第n+1个时钟到来时,向RAM中的第k个单元写数据,同时从第k+1个存储器单元读数据。 读写时钟都是执行同步操作。这样在时钟控制下执行所有的操作。在系统开始工作的第一个时钟到来时,此时写操作指针指向第一个RAM单元,同时的读数据指针指向第二RAM单元。

下面以J.83标准中的卷积交织和解交织器为例来说明。图3是J.83中用FIFO移位寄存器实现卷积交织和解交织的结构图。并行输入数据比特的宽度为8bit。从图中可以看出,交织-解交织器由I个分支构成,从0到I-1,I=12。每个分支的延迟单元数为0、J、2J、......(I-1)J, J=17。每个分支延迟单元数相差为J,所以对所有输入数据来说每个分支的延迟数是不一样的,结果造成对输入数据的延迟不一样,从而完成了交织过程。

通过上面的分析可以看出:用RAM来代替FIFO移位寄存器完成相同的功能。在FPGA和ASIC设计中就可以用单个块RAM代替多个FIFO移位寄存器。根据J.83标准中的结构图可以看出,将整个块RAM按照“FIFO移位寄存器的相应存储单元+1”的大小划分成I个存储小块单元。第0个存储小块大小为1,第一个存储小块大小为J+1,第二个为2J+1,依此类推,第I-1个存储块的大小为(I-1)J+1。在FIFO移位寄存器实现中,由于每隔一个时钟周期,读写指针都要跳到下一个FIFO移位寄存器分支,以实现相应的功能,对于块RAM的存储小块单元来说就是从一个存储小块单元跳到另一个存储小块单元,以实现与FIFO移位寄存器相同的功能。

由J.83的例子可以看出,访问块RAM的读写指针由三个部分组成,第一部分为指示存储小块单元指针,第二部分为小块单元内偏移指针,将这两部分指针相加,得到写数据操作的指针。第三部分是读指针与写指针相比滞后一个时钟周期,并且读地址是写数据指针加1,产生RAM的相应读指针。以便循环读取存储器中的数据。块RAM就根据这些相应的读写指针,写入和读出相应的数据,从而完成了卷积交织。

根据同样的道理可以构造出卷积解交织的块RAM实现方法。从而可以推广到一般的卷积交织-解交织的实现方法,如图4所示。此方法包括下面几部分:小块存储单元切换控制、小块内偏移指针、读时钟延迟一个周期以及小块内偏移指针+1。

小块存储单元切换控制用来选择需要进入的块RAM中的小块存储单元;

小块内偏移指针是用来产生在小块存储单元的偏移地址,它与小块存储单元切换控制所指示的地址相加,可以得到小块内存储单元的写数据地址;

小块内偏移指针+1:将小块存储单元RAM写数据地址+1,就产生了读数据的指针。■

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多