当今的模数转换器 (ADC) 采用了最新的技术,以高精度及快速的采样频率对模拟信号进行采集。数据转换器的复杂性随着采样频率及精度的提高而增加。高性能数据转换器规格的设定必须遵循严格的输入条件,以实现器件预期性能的最大化。一个颇具挑战性的输入条件是:对ADC输入模拟信号进行测量、驱动和接口连接。本文将探讨一些对于高速ADC进行有效接口连接的技术,从而使ADC实现性能最佳化。

就有效输入驱动以维护信号完整性而言,已经有许多好的应用注释以及文章发表。本文将探讨有关输入驱动的新发展。

ADC 输入架构与驱动器的选择

ADC的模拟输入配置随着采样精度和最大采样频率的变化而有所不同。在输入阶段,影响输入驱动器选择的特征有:

1. 单端与差分

2. 高阻抗与低阻抗 (100W) (或是有缓冲与无缓冲)

单端与差分

大部分推动采样精度和采样频率达到极限的ADC采用的是差分输入方式。差分输入的优势在于降低偶次谐波和 EMI。一些差分输入ADC具有IRS(输入范围选择) 寄存器,其允许使用者通过将未使用的输入连接到共模 (CM)A/D转换参照的方式,以单端输入来使用器件。

有缓冲与无缓冲

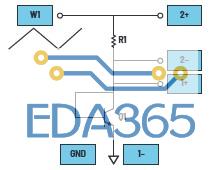

高采样频率ADC (>500 MSPS) 经常要处理高频模拟输入信号。假定使用标准的 PCB板尺寸和轨迹长度,如果这个高频模拟信号没有正常结束,又用处理射频信号和电路板的方式加以处理,模拟信号就会衰退。这样的高频应用得益于低阻抗 (50W单端或 100W差分) 模拟输入,因此,大部分 UHF 和 VHF 电路为 50W系统。为了获得较高的失真性能,通常使用差分输入。由于严格的规范限制,以及受高频的影响,高采样率ADC通常不提供允许使用单端输入的IRS 选项。原因是:采用 IRS 的ADC需要额外的电路才能转换到满量程(FSR),而这对于在高频/高采样率下的应用却并不可行。因此,这个等级的ADC需要高频、低电阻 (100W差分)的输入驱动。使用低电阻输入 ADC,模拟输入在被应用到用于转换的采样/保持 (S/H) 电路之前就已缓冲。所以,并不需要采用在非缓冲 ADC中使用的标准去耦电路 (串联电阻R,并联电容C)。在图1的图解中使用了一个非缓冲输入的 ADC (ADC10080),这些去耦元件在图中标识为 R1、R2(18W) 及 C1 (25W)。

从单端到差分的转换

中点接线变压器

(Ruthroff 变压器)

如前所述,驱动差分 ADC 的输入必须为差分形式。将单端输入转换为ADC 可用的差分信号需要使用一个中点接线变压器,如图1所示(在“差分输入”虚线下可看出变压器如何接到 ADC 输入)。

差分输入的共模电压(CM)应遵循 VCOM 电压(在 ADC 上的输出引脚),以便使 ADC 内部的采样保持电路正常工作。图1中的电路允许通过将变压器的中点接线连接到ADC的 VCOM 输出来对输入 CM 加以设定。

{{分页}}

变压器的较低截止频率不允许低频内容被耦合进来。因此,这种形式的耦合只可应用于不需要 DC 以及低频内容的系统。除此之外,这个电路也承受了高频变压器的泄漏效应,限制了它的上限工作频率。典型的变压器有上限及下限工作频率。较低频率限制由初级电感决定。对于这个与 8 位转换器一起使用的变压器而言,如果不采用其它的增益校准或调整方法,其工作的频带非常窄,受限在 1 MHz ~100MHz,其中,插入损耗变化小于 0.034dB (1 LSB)。

对于最大回波损耗(最小反射),许多较高速度的应用要求对图1中 J1 (输入连接器)处的输入阻抗进行控制,并且要与连接到连接器的电缆特征阻抗相匹配。当电缆的长度超过所遇最短波长的 1/20时,这种要求尤为重要。只要变压器回波损耗在频率极值时性能没有衰退,就有可能通过设置一个通过输入的终端电阻 RT 来达成此目标。这样,输入阻抗就会接近RT,原因在于变压器回波损耗已增大,足以具有最小负载效应。在较高的频率下,由于变压器回波损耗的减少,使用这种类型的变压器配置会使控制输入端更加困难。而这正是不平衡变压器的优势所在。

不平衡变压器

(Guanella变压器)

另一个进行单端到差分转换的方法是使用不平衡变压器,如图2所示。

与图1相比,这种方式具有下述优点及缺点:

优点:

1. 较高的工作频率

2. 对于宽带应用而言,有较高的回波损耗

3. 较佳的增益与相位平衡

缺点:

1. 无法设定共模电压

2. 无法提供电压增益

与图1的中点接线变压器或 Ruthroff 变压器相比,不平衡配置有着更高的工作频率。然而,采用不平衡配置后,因为无法设定共模电压水平,ADC 输入必须为 AC 耦合电压。以ADC08D1500为例,它是一个 8 位、1500MSPS 的转换器,如果在 AC耦合的模式下工作,就会通过内部电阻自动将其输入端偏置到适当的共模电压值。如果ADC的 VCMO 输出接地,就会以 AC 耦合模式运行。

如图2所示,使用 AC 耦合电容 (4.7nF),输入耦合电路的-3dB频率大约为 677 KHz (=1/(2pReqCeq),其中,Req=100W,Ceq=4.7nF/2=2.35nF)。这个 100W的等效电阻是耦合电容器 (RT2与 ADC 的 100W输入并联,总共 50W) 右边的差分负载与介于不平衡变压器引脚1 和引脚3(50W)间差分阻抗的串联组合。

采用图2的电路,J1终止于 50W 左右,并且假定所驱动的ADC具有100W的差分输入终端(如 ADC08D1500)。与 100W ADC输入阻抗并联的 RT2为 50W,这是从 J1 到接地的输入阻抗。此输入阻抗一直保持一定的频率,从而使不平衡变压器发挥变压器的作用。超过这个基于特殊不平衡变压器及其核心特征、线圈间电容,以及其它因数的频率范围,输入阻抗就会偏离这个值,并且输入反射会导致回波损耗减少。大部分不平衡变压器的产品手册都列出了几个频点的回波损耗与上限和下限工作频率。

{{分页}}

图3显示了一个中点接线变压器 (TC4-14) 以及一个不平衡变压器 (TC1-1-13M) 的输入回波损耗,并进行了简单的比较。

{{分页}}

由图3中可以看出,中点接线变压器的回波损耗在 700MHz 以下与 1.3GHz 以上时,下降得十分迅速,而不平衡变压器则具有一定的高出数 MHz 的回波损耗 (> 10dB),并且在频率到达约 2.6GHz 左右时才开始下降。这是不平衡变压器相对于中点接线变压器的优点。在较高频率减少的回波损耗会造成一种不匹配的状态,并且产生较高的反射能量,这会在采集信号中形成不想要的谐波,并且降低系统的 ENOB 性能。

回波损耗 (RL)与 二端口输入阻抗相关,如式1如示:

RL= 20 Log | (Zin+50)/ (Zin-50)| (1)

举例来说,10dB 的 RL 与96W 或 26W的输入阻抗相符合 (根据式1中商的符号而定)。阻抗不连续时的反射波(图2中的 J1)在源端出来另一个反射之后将会抵达 Rs1 (假定来源与传输线并没有完美匹配)。往返时间为 l/n,其中,l为电缆长度,n为通过传输线介质的波速。构成输入信号的不同频率元件,在遇到此往返延迟并且加上原来的入射波之后会回到中断处,从而形成最终的信号。对于往返延迟 (2l/n),l为一个重要的谐波(大约是周期 T 的 1/10),其最终的波形将会失真。从数学上讲,这里的T满足了 T ≤ (20 l/n) 的谐波要求。原因是,对于较短周期的谐波,入射以及反射波会合成(在时间上)交迭形式,这会造成波形的改变。这正是在 ENOB 上降低的原因,因为这个改变的波形将会增加总谐波失真 (THD) 的失真项,从而产生较低的 ENOB。

为了平衡非平衡功能,变压器的初级与次级总会保持1:1 的比例,因此,此配置不能提供任何电压增益。

有源单端到差分的转换

如前所述,变压器可以被用作转换器,然而它们在宽带的应用上有很大的缺点,并且在这些应用中,它们不会在其操作频率区域中包括 DC 和低频。基于这个原因,半导体制造商已经导入了有源器件来执行这项功能,以弥补变压器耦合结构的缺点。

LMH6555 是专门设计用来驱动如图4显示为 0.8Vpp的ADC的 100W差分输入,并且提供一个到终端电缆的固定 50W的输入阻抗(未显示于图4中),以达到最高的回波损耗。单端到差分转换器会将频率范围从DC一直扩展到1.2GHz(此为 LMH6555 的 -3dB 频宽限制)。通过将ADC的 VCMO连接到 LMH6555 的 VCM_REF 输入,可以保持精确的输出共模电压控制。利用这样的结构,可以获得全信号频谱,而共模控制则可以由 LMH6555 自动实现。图4中所示的缓冲器 (LMV321) 用来提高ADC的 VCMO 引脚所流出的电流,以使得对于 VCM_REF输入而言有适当的驱动能力。是否需要缓冲器取决于ADC的电流输出能力。

{{分页}}

LMH6555 的增益(在Vin+下的差分输出到单端或取决于所驱动输入的Vin+)确定在 4.8V/V,其配置如图4所示,其中,Rs1=Rs2=50W。对于输入信号在振幅上较大的情形,LMH6555 插入增益可以通过增加 Rs2和 Rs1的值来降低。这两个电阻应该总是相等,以保持对于低输出偏移的输入平衡。图5所示例子中,位于 50W电缆接收端的 LMH6555 的增益通过 Rx 和 Ry降低。通过选择组件值,LMH6555 电路(J1)的输入阻抗被保持在50W,以使阻抗匹配。两个 LMH6555具有 100W的到地等效阻抗,各个组成值都被显示,以用来维持低输出偏移电压。LMH6555的输入/输出摆幅关系如式2所示:

Vout (Vpp) = Vin (Vpp) * [ RF/ (2Rs+Rin_diff)] (2)

其中,RF= 430W,Rin_diff=78W,都是LMH6555 特定的值。

Rs是等效电阻,使 LMH6555 的输入接地(假定它们相等)。增加 Rs会降低增益。重新整理式2,允许使用者决定 Rs的值,可以确定对于一个给定 Vin (Vpp) 的全ADC的输入摆幅,如式3所示:

Rs=Vin (Vpp) * 268.8 - 39 (3)

在图5中,LMH6555的等效输入电阻通过 Rs被增加到100W(由式3计算得出),因此,0.52Vpp输入会导致ADC输入恰好为 0.8Vpp,而J1的等效输入则维持在 50W。

LMH6555将维持低噪声 (参照19nV/RtHz输出的平带),并与它输入的Rs无关。这是因为 LMH6555 的输入架构由等效输入噪声电压决定,并且独立于源电阻。

ADC要求差分输入的共模电压(在 +/-50mV内)非常接近它所产生的 VCMO 参考输出。这是采用1.9V供电电压的一个结果,因为损失的供电电压降低了ADC内部的电压余量。如果未能保持此共模操作,ADC的全失真性能将会迅速恶化。

除了这种共模现象外,ADC两个输入端的任何增益和相位不平衡都会导致获取错误信号。举例来说,一个 100MHz的方波将会在它的尖峰值有 1.5% 的错误。8 位数据采集具有全尺度 0.39% 的 LSB,并且不平衡变压器等效于3.8LSB。所以,将增益和相位不平衡最小化是非常必要的。

结语

作为高速ADC接口信号的单端到差分转换,对于重要的数据采集任务,本文分析了输入信号接口的挑战,并探讨了不同的技术需求。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多