一、摘要:

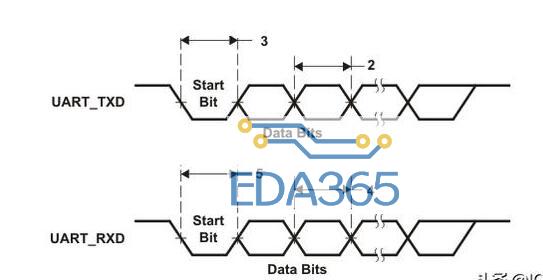

SPI 接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI 时序或是采用带SPI 功能模块的MCU。但随着可编程逻辑技术的发展,人们往往需要自己设计简单的SPI 发送模块。本文介绍一种基于FPGA 的将并行数据以SPI 串行方式自动发送出去的方法。

二、关键字:

VHDL、FPGA、SPI、串行数据输出选择模块、移位脉冲产生模块、SPI 时钟采集信号和无相移的SPI 基准时钟产生模块、SPI 时钟输出选择模块、8bit SPI 时钟采集生成模块、16bit SPI 时钟采集生成模块、24bit SPI 时钟采集生成模块、8bit 数据移位模块、16bit 数据移位模块、24bit 数据移位模块。

三、功能框图:

SPI_MODES 为输入模式选择端口:

--"01"is 8bit 传输模式

--"10"is 16bit 传输模式

--"11"is 24bit 传输模式

CLKS 为整个模块的基准时钟

DBINOUTS 为并行数据输入端口:

--8bit 模式为DBINOUTS(7 downto 0)

--16bit 模式为DBINOUTS(15 downto 0)

--24bit 模式为DBINOUTS(23 downto 0)

SPI_WR 为启动SPI 传输的信号

整个功能模块可工作在 8bit、16bit、24bit SPI 猝发传输状态。对其进行软件操作的步骤相当简单:

--此模块软件操作流程如下

--1、SPI_MODES="xx" 设定串口操作模式

--2、DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" 输入要发射的数据

--3、SPI_WR='0'

--4、SPI_WR='1'

--5、SPI_WR='0'

--8bit 模式延时2*8*4*CLKS

--16bit 模式延时2*1**CLKS

--24bit 模式延时2*24*4*CLKS

--6、DBINOUTS="xxxxxxxxxxxxxxxxxxxxxxxx" 输入下一个要发射的数据

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多