ISL5927是一个双14位,260+MSPS(兆采样每秒),CMOS,高速,低功耗,D/A(数字到模拟)转换器,专门设计用于高性能通信系统,如base使用2.5G或3G蜂窝协议的收发站。

特征

低功率。233兆瓦,130毫秒每秒输出20毫安

可调满标度输出电流。2mA至20mA

保证增益匹配<0.14dB

+3.3V电源

3V LVCMOS兼容输入

卓越的无杂散动态范围(75dBc至奈奎斯特,fS=130MSPS,fOUT=10MHz)

19.2兆赫时,UMTS相邻信道功率=71分贝

EDGE/GSM SFDR=94dBc,11MHz,20MHz窗口

双电源,3.3V,AD9767的低功耗替代品

应用

蜂窝基础设施-单载波或多载波:IS-136,IS-95、GSM、EDGE、CDMA2000、WCDMA、TDS-CDMA

BWA基础设施

中频范围为0-80MHz的正交传输

医疗/测试仪器和设备

无线通信系统

绝对最大额定值热信息

数字电源电压DVDD至DGND。+3.6伏

模拟电源电压AVDD到AGND。+3.6伏

地面,AGND至DGND。-0.3V至+0.3V

数字输入电压(数据、时钟、睡眠)。DVD+0.3V

参考输入电压范围。平均电压+0.3V

模拟输出电流(IOUT)。24毫安

操作条件

温度范围。-40°C至85°C

热阻(典型,注1)θJA(摄氏度/瓦)

LQFP套餐。70个

最高结温。150摄氏度

最高储存温度范围。-65°C至150°C

最高引线温度(焊接10s)。300摄氏度

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这是一个压力等级和操作在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。

注:

1.θJA是用安装在评估PC板上的组件在自由空气中测量的

电气规范AVDD=DVDD=+3.3V,VREF=内部1.2V,IOUTFS=20mA,TA=25 oC(对于所有典型值)

电气规范AVDD=DVDD=+3.3V,VREF=内部1.2V,IOUTFS=20mA,TA=25°C,适用于所有典型值(续)

笔记:

2.增益误差测量为满标度输出电流与通过RSET的电流之比的误差(通常为625微安)。理想情况下比率应该是32。

3.由设计或特性保证的参数,未经生产测试。

4.利用差动变压器耦合输出和无外部滤波进行光谱测量。对于多音测试,相同的模式是用于不同的时钟频率,产生不同的输出频率,但与时钟频率的比率相同。

5.时钟为130MSPS,输出频率为10MHz。

6.时钟200MSPS,输出频率20MHz。

7.时钟260MSPS,输出频率40.4MHz。

8.见“规范定义”

9.建议工作电压为3.0V至3.6V。工作电压低于3.0V可能会导致光谱性能下降。减少为了保持频谱性能,可能需要模拟输出电流。

10.参见典型性能图。

典型性能(+3.3V电源,使用图13,RDIFF=100Ω,RLOAD=50Ω)

规范的定义

相邻信道功率比ACPR是相邻频率通道的平均功率(或偏移量)传输频率信道中的平均功率。串扰,是测量信道与DAC到另一个。它是通过在一个DAC,另一个DAC用静态输入计时,并比较每个DAC在产生的频率。微分线性误差,DNL,是从代码到代码的步长输出偏差。理想的步骤大小应为1 LSB。一个LSB或较少保证单调性。EDGE,全球进化增强数据,TDMA使用200kHz BW的蜂窝应用标准,8-PSK调制载波。通过设置数据输入来测量满标度增益漂移所有逻辑高(所有1s)并测量输出电压通过已知的电阻随着温度的变化从TMIN到TMAX。它被定义为最大偏差从室温下测得的值到在TMIN或TMAX处测量。单位为百万分之一FSR(满标度范围)每摄氏度。满标度增益误差,是理想比值32的误差在输出电流和满标度调整电流之间(通过RSET)。增益匹配,是满标度振幅的测量给定相同输入的I和Q通道之间的匹配模式。通常在两个输入端的所有1s处测量通道和满标度输出电压比较I和Q输出的匹配负载。全球移动通信系统使用200kHz BW的蜂窝应用标准,GMSK调制载波。

积分线性误差,INL,是最差的测量偏离最佳拟合直线数据的实例点沿传输曲线的值。内部参考电压漂移,定义为与房间测量值的最大偏差温度达到在TMIN或TMAX测量的值。单位为ppm/摄氏度。通过将数据输入设置为所有逻辑低(全0)和测量IOUTA的输出电压通过已知的电阻随着温度的变化从TMIN到TMAX。它被定义为最大偏差从室温下测得的值到在TMIN或TMAX处测量。单位为百万分之一FSR(满标度范围)每摄氏度。偏移误差,通过将数据输入设置为逻辑低(全0),测量IOUTA的输出电压通过已知的抵抗。偏移误差定义为IOUTA输出电流与值为0毫安。输出电压符合范围,是电压限制强加在输出上。输出阻抗应为选择这样的电压不会违反符合范围。电源抑制,使用单个电源测量供应。标称电源电压变化±10%,并且注意到DAC满标度输出的变化。参考输入乘以带宽,定义为电压参考输入的3dB带宽。它是经过测量的使用正弦波形作为外部参考数字输入设为1,频率为增加,直到输出波形的振幅原值的0.707(-3dB)。无杂散动态范围,SFDR,是振幅从基本信号到最大信号的差异和谐或非和谐相关的刺激指定的频率窗口。总谐波失真,THD,是RMS的比值基本输出信号与前五个谐波分量。通用移动通信系统用于蜂窝应用的W-CDMA标准3.84MHz调制载波

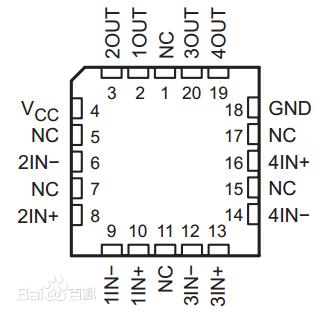

详细说明

ISL5927是双14位、电流输出、CMOS、数字到模拟转换器。最大更新速率至少为260+MSPS,可由一个电源供电建议的电压范围为+3.0V至+3.6V,耗电量为使用+3.3V时,每个通道的功率小于125mW提供最大20毫安的输出电流和数据以210MSPS切换。架构基于减少故障的分段电流源配置通过减少任何时候的电流开关量。在以前包含所有二进制加权的体系结构中电流源或二进制加权电阻梯形图转换器的电流可能会大得多在某些最坏情况下的过渡点打开和关闭例如中尺度和四分之一尺度的过渡。很大程度上减少这些主电源的电流开关量转换时,转换器的整体故障非常严重减少、改善解决时间、瞬态问题和准确度。数字输入和终端ISL5927数字输入格式化为偏移二进制和保证3V LVCMOS电平。内部寄存器是在时钟的上升沿更新。最小化反思,适当终止。如果驱动时钟和数字输入的线路长50Ω线路,则50Ω终端电阻应放置为尽可能靠近连接到数字接地平面(如果使用单独的接地)。这些终端电阻可能不需要,只要数字波形源在DAC的几英寸范围内。对于边缘速率非常高的模式驱动程序,它是建议用户考虑系列终止(50-200Ω)在DAC输入之前,以减少噪音量。

电源

单独的数字和模拟电源推荐。允许供电范围为+2.7V至+3.6伏。建议供电范围为+3.0至3.6伏(名义上+3.3V)以保持最佳SFDR。然而,降低电压至+2.7V是可能的在SFDR。降低模拟输出电流有助于+2.7V时的SFDR。表中规定的SFDR值规格是在+3.3V电源下获得的。地平面应使用单独的数字和模拟地面。设备的所有数字功能及其相应的组件应位于数字地面并终止于数字地面飞机。对于模拟组件和模拟地面。降噪为了尽量减少电源噪声,0.1μF电容器应尽可能靠近转换器的电源引脚,AVDD和DVD。同时,布局设计使用单独的数字和模拟地面电容器应端接至数字接地DVD和AVDD的模拟接地。附加建议对板上的电源进行过滤。电压基准装置的内部电压基准具有+1.23V,漂移系数超过转换器的全温度范围。建议0.1μF电容器应尽可能靠近REFIO引脚,连接到模拟接地。回流管脚选择引用。可以选择内部参照如果回流焊连接在低位(接地)。如果外部参照是所需,则应将REFLO连接至高位(模拟电源电压)和外部基准驱动到REFIO。这个转换器的满标度输出电流是使用的电压基准和RSET值。IOUT应该在2毫安至22毫安范围内,尽管操作低于2mA是可能的,性能下降。如果使用内部引用,VFSADJ将等于大约1.2V。如果使用外部参考,VFSADJ将等于外部引用。IOUT的计算(满标度)为:

如果使用内部电压参考(1.23V)和1.91kΩRSET电阻,则输出电流的输入编码将类似以下内容:

模拟输出

IOUTA和IOUTB是互补电流输出。这个两个电流之和总是等于满标度输出电流减去1 LSB。如果单端使用是需要时,可以使用负载电阻来转换输出电流到电压。建议未使用的输出端接地或同等端接。电压在输出端显影不得违反输出电压符合范围为-1.0V至1.25V。ROUT(阻抗应选择加载每个电流输出),以便所需输出电压与输出满标度电流。如果已知线路阻抗为驱动时,应选择输出负载电阻匹配这个阻抗。输出电压方程为:

降低功率的最有效方法消耗是为了减少模拟输出电流控制供电电流。建议的最大值输出电流为20mA。

差动输出

IOUTA和IOUTB可用于差分到单端排列,以获得更好的谐波抑制。当RDIFF=50Ω且RLOAD=50Ω时,图13中的电路将在如果设置了DAC的满标度输出电流,则为变压器至20mA(用于电气规格表)。价值观RDIFF=100Ω和RLOAD=50Ω用于典型的提高输出功率和动态范围。图13中的中心抽头必须是接地的。在图14中的电路中,用户可以选择研磨或浮动中心丝锥。将存在的直流电压在IOUTA或IOUTB处,如果中心水龙头是浮动的IOUTDC x(RA//RB)V,因为RDIFF被变压器。如果中心抽头接地,则直流电压为0V。图14中电路的建议值为RA=RB=50Ω,RDIFF=100Ω,假设RLOAD=50Ω。图13和图14的性能基本上是同样,但是图14的中心抽头保持浮动允许电路找到更平衡的虚拟接地,理论上改善了偶数阶谐波抑制,但可能会减少信号摆动,因为输出电压符合范围限制。

传播延迟

转换器需要两个时钟上升沿在输出端表示。时钟的每一个上升沿捕获当前数据字并输出上一个数据。因此,传播延迟为1/CLK,加上处理。见图15。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多