特征

最小共模抑制1kV/微秒与LSTTL、TTL和CMOS逻辑兼容宽VCC范围(4.5V至20V)

2.5Mbd保证超温低输入电流(1.6mA)三态输出(无需上拉电阻)保证性能从0°C到85°C滞后安全和监管批准

UL15775000 VRMS,持续1分钟。IEC60747-5-2标准间隙和爬电距离>8.0 mm(选项“T”或“TS”)1414V峰值工作绝缘电压(VIORM)

应用

高速逻辑系统的隔离

计算机外围接口

微处理器系统接口

接地回路消除

脉冲变压器更换

隔离总线驱动器

高速线路接收器

说明

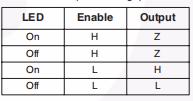

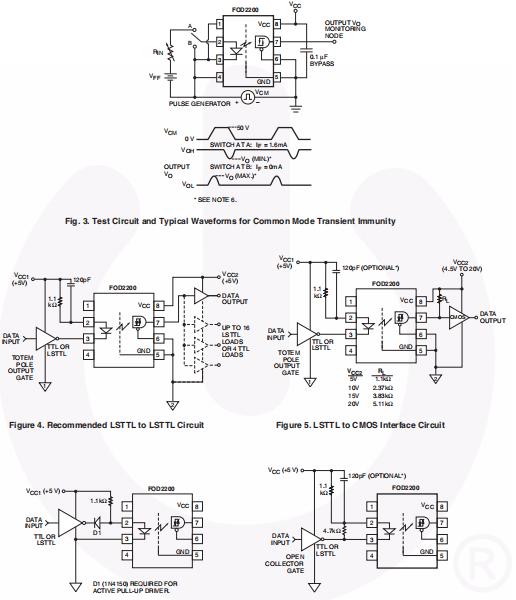

FOD2200是一个光耦合逻辑门结合AlGaAs LED和集成高增益光电探测器。探测器有三态输出并有一个带有滞后的检测器阈值。这个三态输出消除了对上拉电阻的需要,并允许直接驱动数据总线。磁滞提供差模抗扰度和消除输出信号抖动的可能性。的电气和开关特性FOD2200保证在0°C至85°C,VCC范围4.5V至20V。低中频和宽VCC范围允许与TTL、LSTTL和CMOS逻辑降低功耗与其他高速光耦合器相比。逻辑信号以最大传播方式传输。延迟300ns。FOD2200用于隔离高速度逻辑接口,输入输出缓冲线路,并在高位实现隔离线路接收器噪音环境。

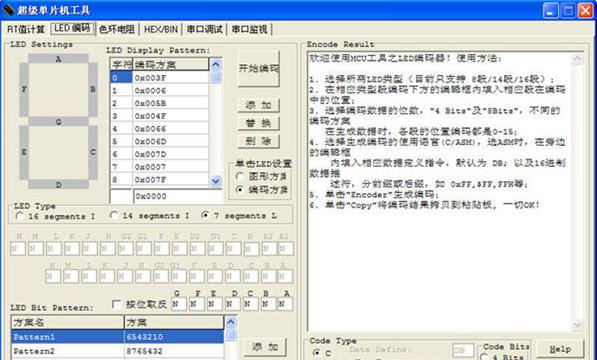

真值表(正逻辑)

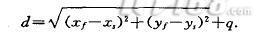

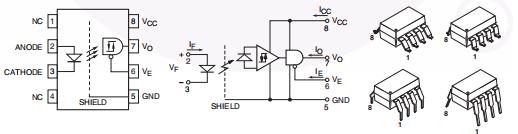

功能框图及原理图

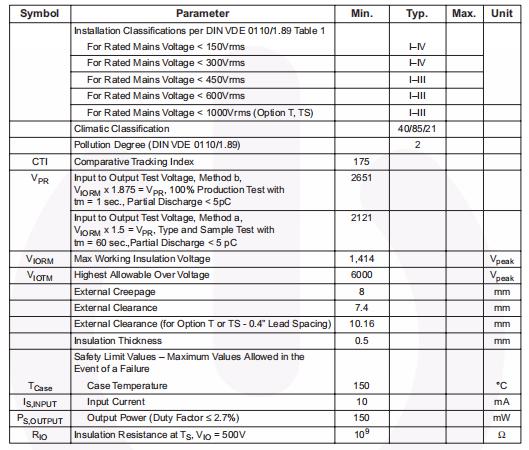

安全和绝缘等级

符合IEC 60747-5-2。此光耦仅适用于安全极限数据范围内的“安全电气绝缘”。应通过保护电路确保符合安全等级。

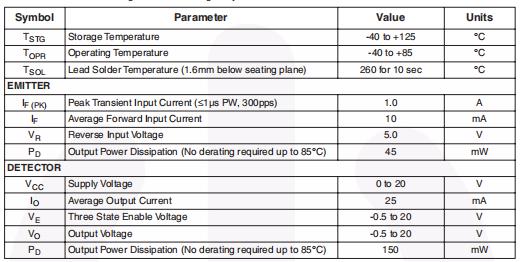

绝对最大额定值(TA=25°C,除非另有说明)

超过绝对最大额定值的应力可能损坏设备。设备可能不工作或不建议在建议的操作条件下操作,并将部件应力提高到这些水平。此外,长时间暴露在高于推荐操作条件的应力下可能会影响设备的可靠性。绝对最大额定值仅为应力等级。

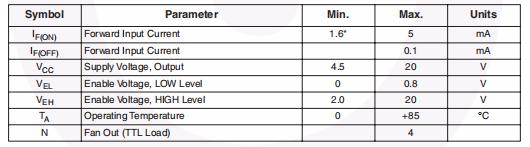

推荐操作条件

推荐操作条件表定义了实际设备操作的条件。推荐规定了操作条件,以确保达到数据表规范的最佳性能。费尔柴尔德没有推荐超过或设计到绝对最大额定值。

初始开关阈值小于等于1.6mA。建议使用2.2mA以允许至少20%CTR降级保护和。

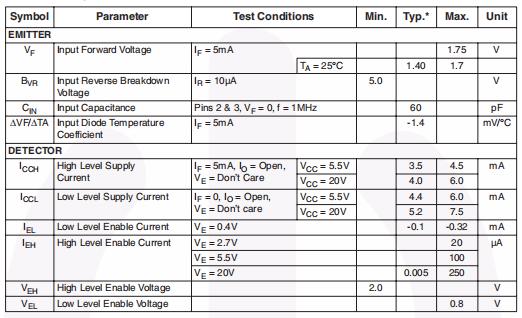

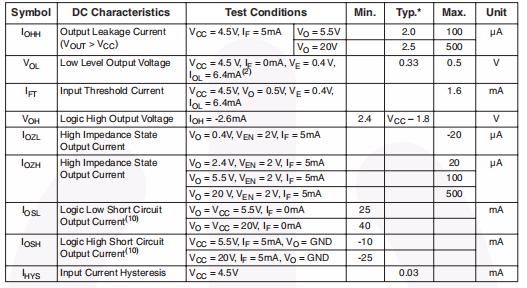

电气特性(TA=0°C至+85°C,VCC=4.5V至20V,如果(开)=1.6mA至5mA,VEH=2V至20V,VEL=0V至0.8V,如果(关闭)=0毫安至0.1毫安,除非另有规定。)(1)

单个部件特性

开关特性(TA=0°C至+85°C,IF(开)=1.6mA至5mA,IF(关)=0至0.1mA,VCC=4.5V至20V除非另有规定。)

电气特性(续)

传输特性(TA=0°C至+85°C,VCC=4.5V至20V,如果(开)=1.6mA至5mA,VEH=2V至20V,VEL=0V至0.8V,如果(关闭)=0mA至0.1mA,除非另有规定。)(1)

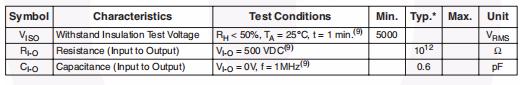

隔离特性(TA=0°C至+85°C,除非另有规定)

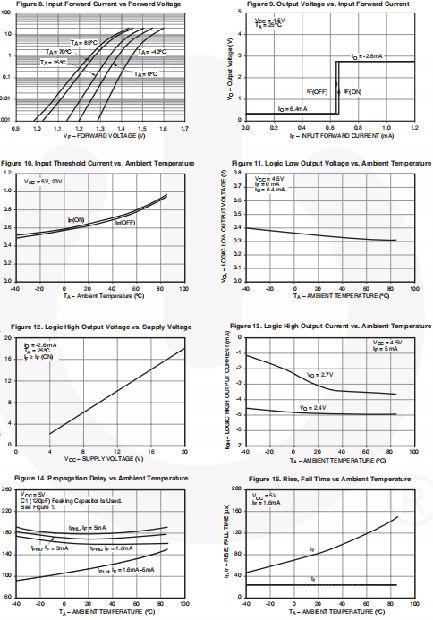

A=25°C,VCC=5V时的典型值,如果(开)=3mA,除非另有说明。

笔记:

1.每个光隔离器的VCC电源必须由0.1μF或更大的电容器旁路。这可以是陶瓷的或具有良好高频特性的固体钽电容器,且应尽可能连接紧密到每个设备的VCC和GND管脚。

2.tPLH–在输入电流脉冲从低到高转换的50%水平上测量传播延迟在输出电压脉冲从低到高的转换上达到1.3V电平。

3.tPHL–在输入电流脉冲从高到低转换的50%水平上测量传播延迟输出电压脉冲从高到低转换为1.3V电平。

4.当省略峰值电容时,传播延迟时间可增加100ns。

5.tr–在输出脉冲从低到高转换时,从10%到90%的电平测量上升时间。

6.转移因子–下降时间是在输出脉冲从高到低转换的90%到10%之间测量的。

7.CMH -共模电压下降的最大可容忍率,以确保输出将保持在高。状态(即VOUT>2.0V)。

8.CML -共模电压上升的最大可容忍率,以确保输出将保持在低水平。状态(即VOUT<0.8V)。

9.被认为是双端装置的装置:引脚1、2、3和4短接在一起,引脚5、6、7和8短接在一起。

10.输出短路时间不应超过10ms。

测试电路(续)

典型性能曲线

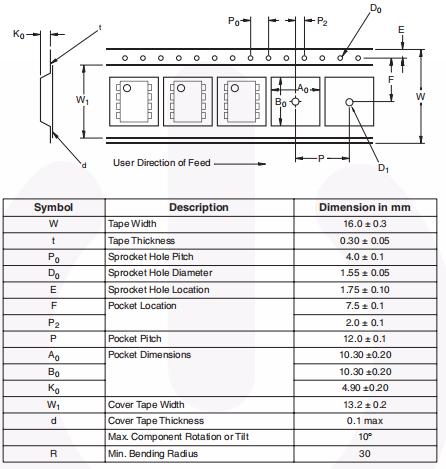

传送带规格(选项SD)

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多