摘要:提出了一种软件无线电通用信号发生器的设计方案,包括硬件构成和软件算法的实现。该信号发生器为软件无线电的研究与开发提供了便利条件。

dsp dds

软件无线电是一种无线电通信新的体系结构。在1992年5月美国电信系统会议上,jeomitola首次提出了软件无线电概念,之后迅速引起了人们的关注,并开始对它进行广泛而深入的研究。具体地说,软件无线电是以可编程的dsp或cpu为中心,将模块化、标准化的硬件单元以总线方式连接起来,构成通用的基本硬件平台,并通过软件加载来实现各种无线通信功能的开放式的体系结构。它使得通信系统摆脱了面向设计思想,被认为是无线通信从模拟到数字、从固定到移动之后的又一次突破。 在软件无线电的研究过程中,调制解调技术是移动通信系统空中接口的重要组成部分。在不同的蜂窝半径和应用环境下,移动通信的信道呈现不同的衰落特性,根据移动信道的衰落情况,自动地改变调制方式,从而提高传输效率并保证传输性能。那么,一个通用的信号源是必不可少的。

图1 多制式信号发生器硬件原理图

作者设计了一个基于dsp+dds结构的可编程调制器的硬件平台,并在此硬件平台上实现了各种模拟调制和数字调制的通用软件算法。当改变调制制式时,无需再次下载程序,而且调制制式、比特速率、输出中频均可调。

1 硬件结构

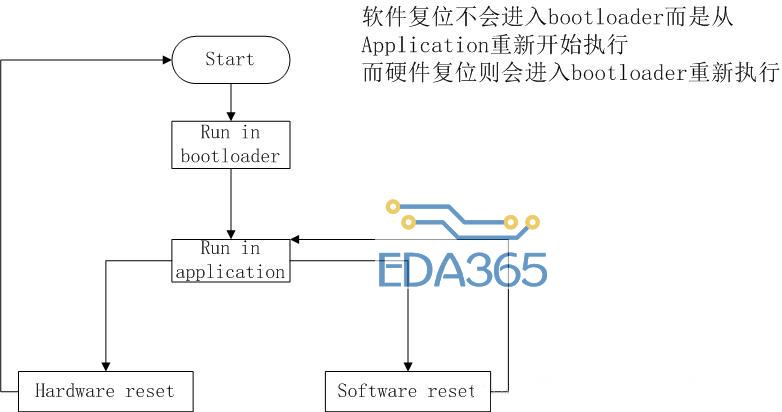

通常,信号源输出的波形多数是对周期的01序列进行调制,输出波形单一,只能作为解调输入信号的一种特例,缺少通用性。而许多专用芯片采用的调制方式也是有限的。用dsp+dds构成的通用多制式信号发生器不仅可以实现模拟调制,而且可以实现各种数字调制。dsp利于基带信号的实时处理,可以实现高速调制,而dds具有频率分辨率高、频率变化速度快、相位连续、易于数字控制等特点。图1给出多制式信号发生器硬件原理图。

信号发生器主要由三部分构成:控制单元、数字信号处理器(dsp)、正交数字上变频器(quadrature digital upconverter)。

dsp采用ti公司的tms320vc5402,它独特的哈佛结构、硬件密集型方案和灵活的指令系统可以满足对信号的实时处理,它的高性能、低功耗及低价位使其得到广泛应用。

正交数字上变频器采用ad公司的ad9857。ad9807最高工作频率为200mhz,输出中频频率范围为0~80mhz。ad9807内部集成半带滤波器、cic(ascaded integrator comb)滤波器、反sinc滤波器、高速的14位是一个相位连续的直接数字频率合成器dds(direct digital synthesizer)。在该方案中,ad9857工作在正交调制模式。它的32位频率控制字使输出频率的最高精确度为:sysclk(系统时钟)除以2 32。 控制单元决定采用哪一种调制制式、比特速率及输出中频频率。

dsp读入控制单元的数据,然后经过串口向ad9857发送控制字。原始信息数据(是由dsp产生的伪随机序列)首先在dsp中进行编码、调制等处理后得到基带信号。基带处理得到正交信号的i/q分量交替进入ad9857,经过串并变换,转换成两路并行的i/q数据,进行内插和上变频运算,然后通过d/a变换直接输出模拟中频信号,从而将基带处理和中频调制合二为一。

ad9857对输入的数字信号进行采样和内插,降低了dsp的处理负担,使整个系统的性能达到较好的程度。

2 软件算法

软件无线电具有完全的可编程性。它采用数字信号处理技术,在可编程控制的通用硬件平台上,利用软件来定主实现无线电台的各部分功能,包括对无线波段、信道调制、接入方式、数据速率的编程等。因此通过程序进行控制和操作,是软件无线电最突出的特点之一。软件算法的设计直接关系到电台软件的实现。软件无线电台对信号的处理都是实时的,因此对算法的时间及空间的复杂性都提出了很高的要求。

为节省有限的dsp运算资源,软件无线电软件算法研究中大量采用查表法来提高处理速度,通常在调制过程中使用波形存储法。编写软件算法程序时,只要某一调制方式及其对应的输出状态数目是有限的,就可以借助表法来实现。查表法避免了大量的中间运算,简单易行,唯一的缺点是占用了大量的存储空间。因此,需要建立一张通用的表格,该表格存储了经过量化的14位有符号的二进制数。表格的设计应达到查表过程简单,同时满足不同的调制方式。用这个表还可以实现正弦函数的计算,只需将当前相位移相π/2。

除了一张通用的余弦表,针对不同的调制方式还需分别建立对应的调制星座图映射表,按照调制方式分类组成一个相位表格库。对于差分相位调制,该表格为差分相位表格。当调制方式确定后,根据得到的码元,查表计算当前相位φk。 图2以(π/4)dqpsk调制方式为例,介绍差分相位调制软件算法。数字存储区存储的是一个周期的余弦函数波形样点,设存储区的采样点数为n,表格的移动步长为d。原始调制每两个比特一组,通过表1中的调制星座图映射成差分相位δφk与前一码无的相位进行模2π相加得到当前码元的绝对相位φk,计算φk在余弦表中的偏移地址,根据偏移地址调制信号的数据。

设f(i)=cos(id),其中0≤i 那么,当前相位φk(0≤φk<2π)的偏移地址为:φk×n/2π。 (π/4)dqpsk对应的绝对相位φk的可能取值有:0°、45、90°、135°、180°、225°、270°、315°。如果n=144,即d=2.5,则φk在余弦表中对应的偏移地址为:0°、18°、36°、54°、72°、90°、108°、126°。表1 调制星座图 3 调制信号波形 采用pcb四层板设计,实现了该信号发生器的硬件平台,并在此平台基础上完成了以下调制方式的软件编程:am、dsb、ssb、fm、gmsk、fsk、bpsk、dbpsk、qpsk、(π/4)dqpsk、8psk、4-64 star-qam。其中数字调制方式的码元速率可达到1mhz(即对于四相调制,比特速率可达2mbps;对于32qam调制,比特速率可达5mbps),载波频率可达到70mhz,调制方式、比特(或码元)速率、输出中频均可调。 图3是用该信号发生器产生的几种调制信号的波形,其中模拟调制以am调制为例,数字调制以dqpsk、fsk、16qam调制为例。 xk 0 0 1 1 yk 0 1 1 0 δφk -135° 135° 45° -45°

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多