摘要:

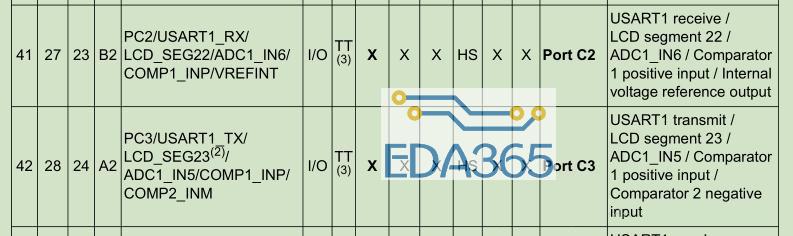

本文描述了用赛灵思公司的XC95216 系列CPLD 芯片实现扩展单片机与计算机PC104 的接口并行通信的方法, 解决了在嵌入式操作系统中单片机与主机总线设备打交道资源不足的固有缺陷, 把以太网卡的功能集成在一片XC95216 的 CPLD 中, 简化了硬件, 通信实时性强; 并给出用VHDL 编写的主要源程序。该方案在实践中检验通过。引 言8位单片机在嵌入式系统中应用广泛, 然而让它直接与PCI 总线设备打交道却有其固有缺陷。8 位单片机只有16 位地址线, 8 位数据端口, 而PCI 总线2.0 规范中, 除了有32 位地址数据复用AD[3- 0]外, 还有 FRAME、IRDY、TRDY 等重要的信号线。让单片机有限的I/O 端口来直接控制如此众多的信号线是不可能的。一种可行的方案就是利用CPLD 作为沟通单片机 与PCI 设备间的桥梁, 充分利用CPLD 中I/O 资源丰富、用户可自定制逻辑的优势, 来帮助单片机完成与 PCI 设备间的通信任务。 1.2 CPLD 设计规划出于对单片机和CPLD 处理能力和系统成本的考虑, 下面的规划不支持PCI 总线的线性突传输等需要连续几个数据周期的读写方式, 而仅支持一个址周期加一个数据周期的读写方式。对于大部分应用而言, 这种方式已经足够了。图1 是经过简化后的PCI 总线读写操作时序。在CPLD 内设有13 个8 位寄存器用来保存进行一次PCI 总线读写时所需要的数据, 其中pci_address0- pci_address3 是读写时的地址数据; pcidatas0- pci_datas3 是要往PCI 设备写的数据; pci_cbe[3- 0]保存地址周期时的总线命令; pci_cbe[7- 4] 保存数据周期时的字节使能命令; pci_data0- pci_data3 保存从PCI 设备返回的数据; pci_request 是PCI 总线读写操作状态寄存器, 用于向单片机返回一些信息。当单片机往pci_cbe 寄存器写入一个字节的时候, 会复位CPLD 中的状态机, 触发CPLD 进行PCI 总线的读写操作; 单片机则通过查询pci_request 寄存器得知读写操作完成, 再从pci_data 寄存器读出PCI 设备返回的数据。 2.2 单片机PCI 读写C 语言程序设计在CPLD 在帮助下, 单片机读写PCI 设备就变得相当简单。首先, 将pci_cbe 等寄存器都声明为外部存储器变量, 并根据CPLD 的设计指定地址。然后, 传递适当的参数给以下两个读写子函数, 即可完成对PCI 设备配置空间、I/O 空间、存储器空间的读写操作。从 PCI 设备的返回数据存放在全局变量savedata 中。实际上在写PCI 设备时, 也可以从pci_data 中得到返回数据。这个数据必须等于往PCI 设备写的数据。利用这一点可以进行差错检验和故障判断, 视具体应用而定。 3 结论用CPLD 实现单片机与PCI 总线接口的并行通信, 电路结构简单、体积小, 1 片CPLD 芯片足够, 并且控制方便, 实时性强, 通信效率高。本设计方法已成功地应用于作者开发的各种数据采集系统中, 用作单片机与PC104 之间的并行数据通信, 效果非常理想。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多