良好的时钟设计是提高数字家庭和汽车娱乐系统音频性能的关键。本文在帮助读者分析了影响时钟准确度和抖动的设计问题之后,详细介绍了一种新型集成式音频编/解码器方案如何为各种音频源产生并选择最好的时钟。

生成并管理准确和低抖动的时钟信号是确保目前数字家庭和汽车娱乐系统质量的关键。典型的A/V设备,如A/V接收器或DVD接收器,必须播放来自大量音源的音频内容。这些设备必须能够从来自VCR的采样模拟音频信号切换到CD播放机的S/PDIF数字输出,或者切换到来自DVD光盘的压缩过的数字音频和视频。为每种音源采用恰当的音频转换器时钟有助于保障最好的音频性能。

就S/PDIF数据流来说,因为用于音频/视频同步和时钟恢复的音频主时钟,如锁相环(PLL),并非是理想的时钟源,所以时钟抖动成为输出高质量音频信号的主要障碍。短到1至2纳秒的时钟抖动就可能引起系统性能的很大下降,使之无法播放宽范围的音频内容(动态范围),并增大谐波失真。

系统动态范围内的失真可以归因于噪音阶的升高。高噪音阶有可能在通过系统扬声器时引起“咝咝”的声音。背景咝咝声在安静的电影画面或古典音乐录音的柔板期间最为明显。而且用不具备足够动态范围的系统所记录的音频节目听起来总是质量很差。

增大动态范围以获取更高的音频信号复制能力并减小恼人的背景咝咝声仅仅是应该关注时钟设计的原因之一。许多消费者目前在购买A/V产品时会追求一定级别的性能和兼容性。

这些消费者尤其感兴趣的两个标志是Dolby Digital和THX兼容标识。这些标识表示承诺了最底线的音频性能和兼容性。但是低劣的音频性能有可能使某种产品无法通过Dolby Digital或THX认证测试。

既然这些和音频性能有很大关系,良好的时钟设计又是提高音频性能的关键,所以了解影响时钟准确度和抖动的设计问题是很重要的。

这些问题开始于音频转换器的主时钟。在一个典型的DVD接收器设计中,视频时钟是基于晶体振荡器的,而且为了维持音频和视频之间的适当解码,音频时钟要根据采用PLL电路的视频时钟来合成。PLL的灵活性还可用来在音频流内容改变时产生正确的音频转换器时钟频率,例如,从用于DVD的48kHz音频转换到用于CD播放的44.1kHz。由PLL合成的时钟成为产生音频时钟的唯一源头。

为了节省成本,许多芯片公司把PLL集成到DVD处理器之中。然而,由于不恰当的芯片布局布线设计、高频率的开关噪音或者低劣的电源线隔离设计,PLL的输出可能包含相当数量的宽频抖动。即使大部分PLL的设计采用了大量的数字逻辑电路,但从根本上讲它们还是模拟系统。这意味着一个抖动的PLL不会与芯片上的其它数字电路和谐共存。良好的PLL设计依靠混合信号技术,并且需要熟练的混合信号设计师所用的设计方法学。

PLL产生的主时钟接着再分配到各个离散的元件上,如用于播放的D/A转换器,用于音频信号采集的A/D转换器,以及用于数字接口的S/PDIF接收器。理解并均衡这些信号负载及相关的电路板布线是维持高速主时钟完整性的关键。现在还必须考虑阻抗匹配和传输线效应,以便减少时钟边缘的可能反射。

不同的公司采用不同的策略以应对不良的时钟性能。对低成本产品而言,制造商一般只要勉强通过Dolby确定的要求即可,同时允许来自模拟源的音频、来自CD的数字音频以及来自S/PDIF等数字接口的PCM的性能可以差一些。这种方法在成本考虑优先于高质量音频时可能很有意义。

对于中档A/V产品而言,Dolby和THX认证是重要的,总体音频性能也很重要,一些设计人员选用更高分辨率的D/A转换器和A/D转换器来增加动态范围,尽管这也许会降低对时钟抖动的敏感性。

在这种情况下,就希望能有更大的设计裕量,以便克服由于时钟抖动引起的性能下降。但是更高分辨率D/A转换器和A/D转换器的成本也会更高,而且也许会需要额外的电源滤波和运算放大器缓冲。使用这些技术的A/V产品经过仔细设计可以减少时钟抖动源,当然,设计时间和电路板的复杂度都增加了。另一项实现高质量PLL的技术就是使用片外分立元件。这会需要额外的卡逻辑电路,它不仅会增加系统成本,而且其本身可能成为一个时钟抖动源。

采用恰当的时钟

为每个音频源配置一个主时钟源并不总是最好的解决方案。例如,在DVD接收器中一般有三个音频源。一个音频源是来自VCR、摄像机或电视的模拟音频。这些模拟音频源转换成数字音频,并针对Dolby Pro Logic/Pro Logic II和低音管理等特性进行后处理。由于对这些源完全不需要视频同步,因此这种情况下使用的最好时钟是一个振荡器。高质量振荡器被认为是低抖动时钟的最佳来源。

音频内容的另一个来源是提供PCM或压缩AC3多通道音频的S/PDIF数字接口。典型的例子包括CD播放机、卫星接收器或电视机顶盒。来自S/PDIF接口的数字音频也可以针对Dolby Digital/Pro Logic/Pro Logic II 、DTS和低频管理等特性进行再处理。对合适的数据提取而言,PLL可用来锁住嵌入的时钟信息,并复原S/PDIF数据流中的时钟信号。复原的PLL输出时钟可用作系统中所有D/A转换器和A/D转换器的主时钟。

DVD接收器中的第三个音频源是来自于CD/DVD光盘的数字音频采样,或是来自DVD光盘或IEEE1394接口的压缩音频和视频信号。这种情况下的最佳选择是一个高性能、低抖动PLL。

理想情况下,DVD接收器应该使用最适合于客户所选音频源的时钟。这样做的一种方法就是采用新一代集成音频编/解码芯片,如Cirrus Logic公司的CS42528。这种新型的编/解码芯片具有高水平的部件集成度,可以支持常见的消费电子产品功能,如带有2通道A/D转换器,6或8通道D/A转换器,一个S/PDIF接收器,全都能支持高达192kHz的采样速率。在一个典型DVD接收器设计中,CS42528可以和一个DVD处理器配对使用,如Cirrus Logic的CS98200处理器。

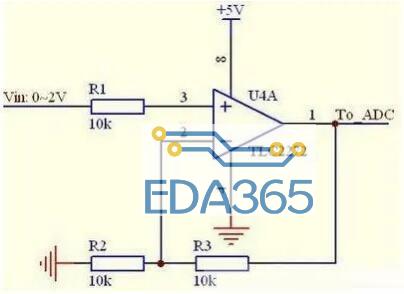

对于模拟音频源(电视,VCR或CD播放机)来说,一个连到CS42528芯片OMCK管脚的12.288MHz振荡器可以提供内部D/A转换器和A/D转换器所用的低抖动音频主时钟。RMCK时钟输出管脚可以配置成把此音频主时钟信号提供给CS98200。CS98200音频处理器和音频串口必须利用此时钟来实现与A/D转换器输出数据率的同步操作。按照后处理算法,音频数据采样随后送到CS42528上的D/A转换器用于播放。音频数据的采样率是可调的,其范围在32kHz到192kHz之间。

由于A/D转换器和D/A转换器所用的振荡器时钟就在芯片附近,全部逻辑和走线对部件来说都是内部的,而且其设计考虑就是把任何潜在的抖动源最小化,最佳性能才能得以实现。>

当选择把压缩过(IEC61937)或PCM(IEC60958)数字音频源连接到S/PDIF口时,CS42528的集成化PLL可复原S/PDIF数据流中的时钟信号。提取出来的低抖动时钟可用于驱动内部的D/A转换器和A/D转换器,而且可以在CS42528的RMCK管脚上出现。PLL输出的时钟频率是输入采样率的256倍。一个48kHz的输入数据流将产生一个12.288MHz的音频主时钟。

把干扰降到最低

CS42528的模拟、数字和PLL部分的设计已经把数字开关电路对敏感模拟元件的干扰降到最低。关键的时钟管理电路提供了时钟边缘控制,从而把开关效应降到最低。分离的电压供电管脚,再加上适当注意接地结构和返回电流,可以把PLL输出上的抖动源降到最低。在PLL输出上测到的典型时钟抖动只有150皮秒。

DVD处理器将此时钟用于音频处理,并保持与S/PDIF数字接口上的输入数据率同步。按照所需的任何解压缩和/或后处理算法,音频数据采样随后送到CS42528上的D/A转换器进行播放。S/PDIF接口可以支持32kHz到192kHz的采样率。

因为实际的S/PDIF接收器、PLL、D/A转换器和时钟开关电路集成在单一芯片上,所以对引脚数目、板走线长度、阻抗匹配以及高速信号的传输线效应等常规考虑就不再那么重要了。系统内时钟抖动的来源显著减少了,其结果就是一个能产生高质量音频的音频时钟。

DVD处理器中集成的PLL合成了音频主时钟,其工作频率一般为12.288MHz或24.576MHz。通常在这个时钟上出现的抖动会引起D/A转换器的动态范围下降,并引入谐波失真。

为了把DVD处理器内主时钟抖动的影响降到最低,CS42528编/解码器的一个特性就是允许其内部的PLL锁到输入数据采样时钟,即DVD处理器的AUDO_LR管脚上,并产生一个到D/A转换器的内部主音频处理时钟。通常,该编/解码器中集成的PLL用于在接收来自S/PDIF接收器的数据时提取嵌入的时钟信息。

抖动的抑制

CS42528中集成的低抖动PLL可复用于DVD和音乐CD的播放,其做法就是选择把该内部PLL的输入锁进SAI_LRCK输入脚上的帧信号之中。由于此DVD处理器AUDO_LR脚上的采样速率时钟取自DVD处理器内部PLL的输出时钟,它含有一定量的抖动,所以可以预料SAI_LRCK信号也含有抖动。然而,由于SAI_LRCK信号的频率通常比PLL输出时钟频率低128、256或512倍,所以它所存在的抖动量相对于SAI_LRCK采样时钟的周期而言是微不足道的。

CS42528的PLL在输入的SAI_LRCK信号上实现了非常好的抖动抑制,进而产生一个低抖动的输出时钟。

CS42528内部的PLL可以支持SAI_LRCK的采样频率有32、44.1、48、88.2、96、176.4 和192KHz。连接到SAI_LRCK的AUDO_LR采样率时钟信号将锁定在27MHz主时钟,并作为CS42528内部PLL的输入。有了这种联系,CS42528内部产生的主音频时钟将锁定在系统的27MHz主时钟,因而只带有非常少量的抖动。

由于PLL和时钟开关电路都集成在CS42528编/解码器内,PLL使用采样率时钟来产生转换器主时钟,因而系统内的时钟抖动源显著减少。若采用这种时钟安排以及48kHz的采样频率,测试结果表明一个D/A转换器有108dB的动态范围,DVD处理器主时钟上的宽带抖动为700ps。当D/A转换器直接由DVD处理器主时钟提供时钟的话,其动态范围性能会退化到89dB。

通过使用一片集成式音频编/解码器,就可为音频源产生并选择最好的时钟。对模拟源来说,振荡器控制的主音频时钟是最佳选择。对来自CD播放器、机顶盒或卫星接收器的数字音频来说,片上低抖动PLL将根据输入的S/PDIF数据流来产生主音频时钟。而对于来自CD或DVD盘的数字音频数据,以及来自DVD盘 或IEEE-1394口的压缩A/V数据来说,该片上PLL将根据DVD处理器串行音频左/右时钟里的采样率信息产生一个低抖动时钟。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多