场制发射显示器(Field Emission Display,FED)是一种新型的平板显示器件,具有反应速度快、重量低、功耗小、视角大、颜色鲜艳等优点,是继LCD,PDP,OLED等之后的另一种最有前途的新一代平板显示器。目前我们研制出的25英寸彩色大屏幕印刷式场致发射显示器,在国内外属于首创,同时研制出可实现场致发射显示器图像显示的集成驱动电路系统。随着可支持分辨率的提高,系统中数据传输的速度也相应地加快。在信号的传输过程中,高频率的信号很容易受到外界信号及杂波的干扰。假如这些信号受到干扰,那么整体的图像质量就会下降,甚至影响整体的稳定性。考虑到存在的问题,我们采用了低压差分信号技术(LOW Voltage Differential Signaling,LVDS)。他具有高速传输、低功耗、噪声控制、低成本等优点,目前已经广泛应用在电信通讯、数据通信和显示设备上的点对点通信应用中。实验证明,使用LVDS可以很好地解决信号传输过程中受到的干扰问题。

1 FED主板接口中信号的传输

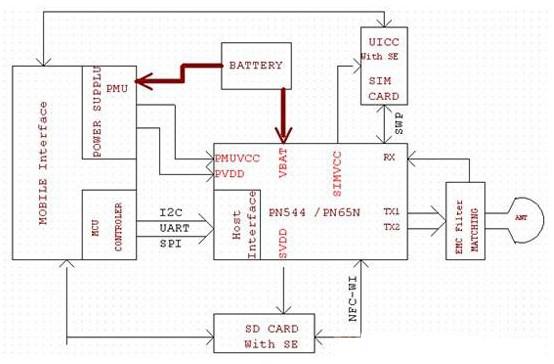

FED电路系统主要由视频接收单元、视频A/D转换单元、数据缓存单元、集成灰度调制驱动单元、行后级集成驱动单元、FPGA控制模块单元和电源模块等部分组成[1]。

视频信号经过SiI161解码以及FPGA图像处理分离出来的三基色RGB数据信号、数据使能CSI、移位数据时钟SC、计数时钟CC和计数使能LC信号要传送到后级灰度调制系统,作为控制信号供给后级驱动芯片HV632使用。信号的传输主要是指主板接口和行、列板接口电路之间的数据传输。信号在普通数据线传输过程中,很容易受到外界信号的干扰,尤其是三基色RGB数据信号,目前的VGA分辨率系统后级数据时钟采用10 MHz,传输速度快,这样的速率在传输过程中更容易受到干扰。如果数据信号受到干扰,那么在屏幕显示的图像质量则会受到影响。如果后级驱动芯片的控制信号受到干扰,那么画面就会产生抖动,受到的影响就会更大。考虑到FED以后的分辨率会增大,那么数据传输速率会变得更快,所以在信号传输过程中受到干扰的机会就会越来越大。那么使用LVDS接口来进行数据传输,刚好可以解决信号传输所受到的干扰问题。

2 LVDS接口的原理及特点

2.1 LVDS的工作原理

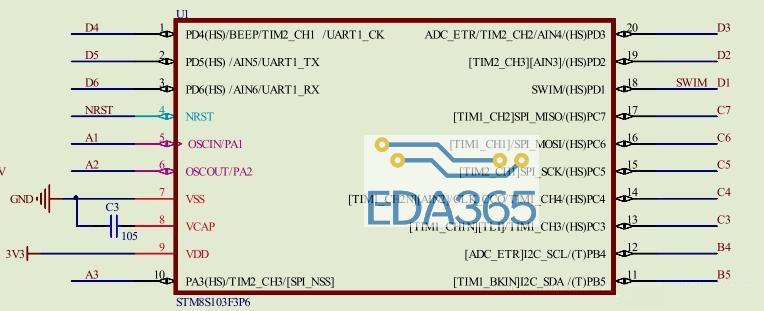

LVDS电路由发送器和接收器以及终端匹配电阻组成,M1,M2,M3,M4是尺寸、工艺都相同的NMOS管开关。发送器的输出接在阻值为100 Ω的终端电阻上,构成回路。驱动器工作时,NMOS开关M1和M4以及M2和M3在CMOS信号的作用下轮流导通和截止,在输出端产生±3.5 mA的回路电流。绝大部分发送电流将流经100 Ω的终端电阻,并在接收器输入端产生大约350 mA的压降。当发送状态翻转时,流经电阻的电流方向改变,于是在接收端产生了一个有效"0"或"1"的逻辑状态。从而把一个CMOS信号转换成了LVDS信号。

2.2 LVDS的优点

应用LVDS具有许多优势:

速率高 在ANSI/EIA/EIA-644定义中的LVDS标准,理论极限速度为1.932 Gb/s,由于LVDS逻辑状态间的电压变化仅为350 mV,因而能非常快地改变状态。

功耗低 随着工作频率的增加,LVDS的电源电流仍保持3.5 mA,同时也限制跳变期间产生的任何尖峰电流。当终端匹配电阻为100Ω的时候,功耗仅为3.5 mA×350 mV=1.225 mW,而且功耗是恒定的,不像CMOS收发器的动态功耗那样相对频率而上升。

噪声性能好 LVDS输出的差分信号固有的优点就是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减,从而可消除噪声,而且由于差分信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合得越紧密,释放到外界的电磁能量就越少,降低了电磁干扰。

具有故障安全(fail-safe)特性确保可靠性 因为恒流驱动解决了损坏问题,所以LVDS发送器和接收器还能实现热拔插[2]。另一特点是接收器的故障保护功能,LVDS接收器在内部提供了可靠性电路,保证在接收器输入悬空、接收器输入短路以及接收器输入处于发送器三态输出或供电终止等情况下输出可靠,防止产生输出振荡。

3 LVDS在FED中的实现

3.1 LVDS芯片选型

LVDS芯片主要有发送器和接收器两个部分,发送器和接收器主要完成TTL信号和LVDS信号之间的转换。在具体的LVDS芯片选型中,采用了美国国家半导体公司的DS90CF383A和DS90CF384A,其中DS90CF383A作为发送器,DS90CF384A作为接收器。该芯片是用于显示接口和平板显示连接的专业芯片,他可以提供更高的分辨率和更高长的电缆驱动[3]。此芯片采用56脚FSSOP封装,体积小,工作电压为+3.3 V,传输速度高达65 Mb/s,完全符合设计需要。

DS90CF383A/384A具有以下特点:

支持20~65 MHz移位时钟;具有节能模式,功耗小于130 mW;支持VGA,SVGA,XGA和SXGA格式分辨率;高达1.8 Gb/s的吞吐量;高达227 MB/s的带宽;自身锁相环无需附加电路;兼容TIA/EIA-644LVDS标准。

发送芯片可以支持24 b的数据位传输和4位控制信号在一个时钟周期内转换成混合的4组LVDS数据流,同时在第5组LVDS链路上将象素移位时钟信号(FP-SHIFT/CK)发送出去,时钟信号的每个周期都将对上述28位数据和控制信号进行采样和发送。为了方便使用,发送器可通过一个专门引脚设置为上升或者下降沿触发。具体连接方式如图3所示。

3.2 芯片具体应用

由于DS90CF383A共有28个信号输入,根据芯片引脚的排布,将TxIN27和TxIN0~TxIN6作为R的8位信号输入端;TxIN7~TxIN14作为G的8位信号输入端;TxINl5~TxIN22作为B的8位信号输入端;剩下4位TxIN23,24,25和26分别作为数据使能CSI、移位数据时钟SC、计数时钟CC和计数使能LC信号,这4位控制信号供给后级灰度调制系统的HV632芯片工作。TxCLK IN则接40 MHz的时钟;VCC端接+5 V,LVDS电源和锁相环电源均接+3.3 V;其中模拟地、LVDS地和锁相环地分别用磁珠隔开,以减小干扰。

芯片的第17引脚R_FB作为触发方式选择,当接高电平时,为上升沿触发,当接低电平或者悬空的时候,为下降沿触发。本设计中令其接低电平,使芯片工作在下降沿触发方式。工作时,由于R_FB引脚接了低电平,所以数据位TxIN 0~TxIN 27在输入时钟信号的下降沿载入移位寄存器,TxCLK IN输入的时钟频率经过锁相环倍频7倍,分别送给4个移位寄存器用来取出每个寄存器中的7位数据;时钟信号也同时变成一对差分的时钟信号Tx-CLK OUT+和TxCLK OUT-,TxCLK OUT输出的时钟周期则和输入的TxCLK IN的周期是一样的,都为一个时钟周期TCLK,只是时钟的输出比输入延时约5.5 ns。当POWER DOWN信号为低的时候,经过一个100 ns的TPDD(Transmitter Power Down Delay)延时,4路串行数据流和一对差分时钟信号从LVDS发送器发送。在一个时钟周期内,5个串行输出口同时输出,其中TxINO~Tx-IN27按照特定的顺序分别从TXCLK OUT0~TxCLKOUT3输出。

接收芯片DS90CF384A则是接收发送器送出的串行数据流并将其转换成并行数据输出。和发送芯片DS90CF383A一样,同样设置下降沿触发以及40 MHz时钟,这样在一个时钟周期内,可以把接收到的4路串行数据流转换成28路并行数据信号,并且在相对应的管脚输出。这样,要传送的信号就能够完整地在接收端还原出来。

在传输过程中,由于传输距离约为1 m,所以选择了双绞线对。虽然用普通数据线也可以传输信号,但就减少噪声和提高信号质量而言,平衡电缆(如双绞线对)通常比非平衡电缆好。电缆长度小于0.5 m时,大部分电缆都能有效工作;距离在0.5~10 m之间时,CAT3双绞线对电缆的效果较好;在距离大于10 m并且要求高速率时,建议使用CAT5双绞线对[4]。因此,考虑到信号传输距离只有1 m,所以最终选择了CAT3双绞线对作为传输媒介。

3.3 PCB布板

在LVDS的PCB布板中,主要考虑4点因素,分别是差分走线、阻抗匹配、串扰问题和电磁干扰(EMI)。差分走线 对差分布的越近越好,避免差分走线阻抗不均匀;整个走线工程应该保持差分线的宽度和长度保持一致,否则会导致终端相位有差异,会降低系统的性能;应用135°角走线代替90°脚走线,防止在拐角尖端发出电磁波产生干扰。

阻抗匹配 阻抗不匹配将导致共模噪声的增加并且产生电磁干扰(EMI),所以应该选择匹配电阻和差分线的阻抗相一致;在发送端放一个匹配电阻(100Ω);终端阻抗与终端的距离应尽量小,尽可能地靠近接收端。

差分信号和单端信号的串扰 为了避免单端信号和LVDS信号产生串扰,应尽量使二者分层。如果单端信号与差分信号走的太近,将会产生共模噪声,从而造成接收端的假发射,降低信号的质量,减少信号的噪声冗余量。

电磁干扰(EMI) 单端传输(TTL、CMOS)所有暴露的线都能产生辐射,LVDS走线成对出现,产生的电磁波能够彼此相互削弱,只有在边缘区域才能产生逃逸的现象,因此LVDS走线作为传输系统对单端传输电磁干扰较少。

4 实验结果

经过使用LVDS接口,信号在传输过程中受到的干扰变小了,图像质量也有了进一步的提高。在使用LVDS接口以前,在屏上显示的图像经常有列方向的干扰,例如在底色为黑色的地方会出现其他颜色,显示质量被降低了很多,如图5所示;在使用了LVDS接口以后,图像上的干扰明显减少。

5 结 语

LVDS技术已经在PDP,LCD等平板显示器上获得了成功,并且目前技术已经相当完善,在合理的信号处理及后级驱动的基础上,把这种接口技术引入FED,正是解决干扰和提高显示质量所需要的。本设计就LVDS的原理和特点进行了介绍,并根据其优势特点实现了在FED中的应用。目前已研制出的FED样机亮度410cd/m2, 对比度1010:1灰度256级。本设计所用的SD90CF383/384套片是平板显示器专用的一套芯片,除了此套芯片外,也可以用SN75LVDS83/82代替

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多