数字滤波器是一种用来过滤时间离散信号的数字系统,通过对抽样数据进行数学处理来达到频域滤波的目的。根据其单位冲激响应函数的时域特性可分为两类:无限冲激响应(IIR)滤波器和有限冲激响应(FIR)滤波器。与IIR滤波器相比,FIR的实现是非递归的,它总是稳定的,更重要的是,FIR滤波器在满足幅频响应要求的同时,可以获得严格的线性相位特性。因此,它在高保真的信号处理,如数字音频、图像处理、数据传输以及生物医学等领域得到广泛应用。然而,数字滤波器的应用场合大部分都要求实时处理,有的还要进行复杂运算,在处理速度方面,FPGA表现出了特有的优势。实践表明,用FPGA来实现32阶8位的FIR滤波器速度可达到每秒100兆以上。此外,FPGA还具有开发周期短、开发软件投入少等优势。

FIR滤波器结构与原理简要

N阶的FIR滤波器系统的传递函数为: (略)(1)

它有N-1阶极点在z=0处,有N-1个零点位于有限z平面的任何位置。(1)式的系统差分方程表达式为

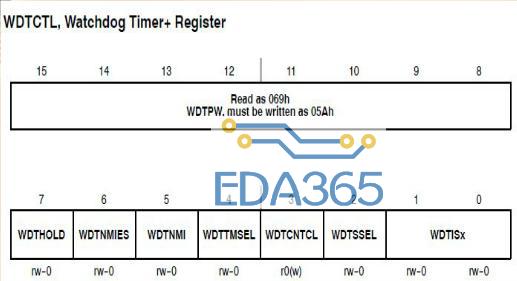

(略)(2) 上 式就是序列x(n)与单位冲击响应h(n)的线性卷积。由上式可知, n时刻的输入y(n)仅与n时刻的输入以及过去N-1个输入值有关。因为直接型结构简单直观,当具有系数对称结构时,总运算量可减少一半,且系数调整方便,故硬件实现较多的采样直接型结构,可以直接画出其网络结构,如图1所示。如果FIR滤波器的单位冲击响应h(n)对称,例如单位冲击响应满足: 则该因果系统具有严格的线性相位。当M为偶数时,(2)式可化为:

(略)(4) 同理,当M为奇数时,(2)式可化为: (略)(5)

FIR滤波器的参数设计

设计要求

数字滤波器实际上是一个采用有限精度算法实现的线性非时变离散系统,它的设计步骤为:先根据需要确定其性能指标,设计一个系统函数H(z)逼近所需要的技术指标,最后采用有限精度算法实现。采用窗函数法设计一个FIR低通滤波器的设计指标为: 采样频率:25M;截止频率1M(0.08π);通带最大衰减?1dB;阻带最小衰减?30dB。理想低通滤波器的截止频率为1M,由于窗函 数主瓣的作用而产生过渡带,出现了通带截止频率W1和阻带截止频率W2 。阻带截止频率:3M;选择Blackman窗可计算得到,窗口长度N=50+1=51;设计频率选择性数字滤波器时,通常希望能有近似恒定的频响幅度,并尽量减小通带内的相位失真,斜率为整数的线性相位对应于时域中简单的延时,它在频域中可将相位失真降到最低的程度,用Matlab提供的滤波器设计的专门工具箱——FDAtool仿真设计滤波器,满足要求的FIR滤波器幅频特性。 把获得的滤波器系数导出为文本文件保存。 FIR 滤波器算法模型建立及仿真

模型建立

根据FIR滤波器原理,可以利用FPGA来实现FIR滤波电路,设计流程的第一步是在Matlab/Simulink中进行设计输入,即在Matlab的Simulink环境中建立一个MDL模型文件,用图形方式调用Simulink库中的图形模块,构成系统级或算法级设计框图(或称Simulink建模)。其中FIR滤波器的参数由在FDAtool中获得的参数加载进去。

系统级仿真

输入信号采用频率分别为f 1 =2MHz和f 2 =5MKHz的两个正弦信号进行叠加,从FIR滤波电路的仿真结果看出,输入信号通过滤波器后,输出基本变成单频率的正弦信号,至此完成了模型仿真。在simulink里运行结果如图3所示。 上面两个为输入的正弦信号,第三个为叠加后的信号,最后一个为滤波后的结果。纵轴为信号幅度,横轴为示波器的采样时间。在此只截取了部分时间结果。

基于FPGA的数字滤波器的实现

为了缩短设计周期,利用FPGA自带的IP核进行滤波器的设计,输出取高位。把以上设计的系数加载到IP核中。

生成VHDL代码。通过编译后下载到FPGA中(ALTERA Cyclone EP1C12Q240C8)。利用信号发生器产生的f 1 =2MHz和f 2 =5MKHz两个正弦信号进行叠加,用FPGA实现的数字滤波器处理的是数字信号,在实际应用中,首先就要用A/D转化器对模拟信号进行采样与量化。本设计通过AD9288采样量化,设置模式为Normal,输出为二进制补码。通过SingnalTap逻辑分析器,读取并保存结果。 上两部分为输入的信号,第三部分为信号叠加后未滤波的结果,最后一部分为滤波后的结果。横轴为采样点的个数,纵轴为幅度(转换的部分程序如下)。 clear,clc; a='0110101。。。。' % fid = fopen('111.txt', 'r');% for i=1:131072 % a(i)= textscan(fid, '%1s', 1); % end;b=zeros(1,8); for i=1:1000 for j=1:7 b(1)=str2num(a(i*8)); if b(1)==0 b(9-j)=str2num(a((i-1)*8+j)); c (i)=(b(2)*2^6+b(3)*2^5+b(4)*2^4+b(5)*2^3+

b(6)*2^2+b(7)*2^1+b(8)*1);

end; if b(1)==1 b(9-j)=~str2num(a((i-1)*8+j)); c (i)=-1*(b(2)*2^6+b(3)*2^5+b(4)*2^4+b(5)*2^3+b(6)*2^2+b(7)*2^1+b(8)*1+1); % fclose(fid);

结束语

用信号发生器产生所要求的两个不同频率的正弦信号,就可以在示波器上看到滤波以后的结果,需要设计不同的滤波电路时,仅修改滤波器模型文件就可以实现。可见在利用FPGA进行数字滤波器的开发时,采用FPGA的IP核作为工具能快捷、可靠地设计实用滤波系统。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多