数字 IC 设计流程是每个 IC 从业者的第一课,无论你是做前端,后端,还是验证,都需要对芯片的整个设计流程有个基本的了解。

本文章主要介绍以下三点内容:

一 . 数字 IC 设计的流程及每个流程需要做的工作

二 . 每个流程涉及到的 EDA 工具

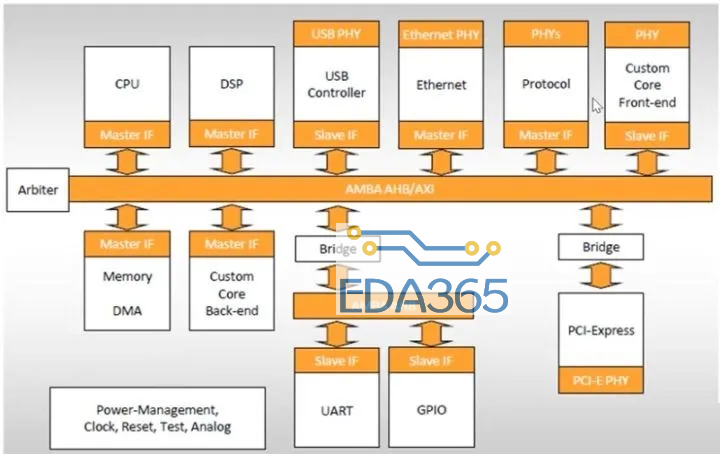

在介绍设计流程之前,我们先来看看数字芯片内部的架构。

如下图所示,一个芯片是包含很多模块的,有 CPU,DSP,USB 外设,memory 等,然后通过总线连接,1 通常我们都是把各个模块先设计好(IP team),然后再把他们集成到一起(SOC team).

一 . 数字 IC 设计的流程

下面我用流程图把设计的四大步以及要做的事情整理出来,主要分四大步:

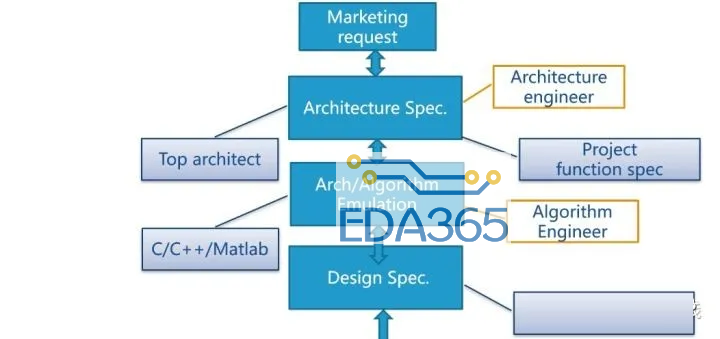

1. 确定项目需求

首先做一款芯片需要有市场,一般公司会先做市场调研,比如最近市面上比较火的人工智能芯片,物联网芯片,5G 芯片,需求量都比较大。有了市场的需求我们就可以设计芯片的 spec 了。先由架构工程师来设计架构,确定芯片的功能,然后用算法进行模拟仿真,最后得出一个可行的芯片设计方案。

有了芯片的 spec,下一步就可以做 RTL coding 了。

2. 前端设计

RTL(register transfer level) 设计:利用硬件描述语言,如 VHDL,Verilog,System Verilog, 对电路以寄存器之间的传输为基础进行描述。

功能仿真:通常是有 DV 工程师来完成这部分工作,通过搭建 test bench, 对电路功能进行验证。

逻辑综合:逻辑综合是将电路的行为级描述,特别是 RTL 级描述转化成为门级表达的过程。也就是将代码翻译成各种实际的元器件。

STA:(static timing analysis) 静态时序分析,也就是套用特定的时序模型,针对特定电路分析其是否违反设计者给定的时序限制。

整个 IC 设计流程都是一个迭代的过程,每一步如果不能满足要求,都要重复之前的过程,直至满足要求为止,才能进行下一步。

除了以上的步骤,前端设计还有一个步骤就是 DFT,随着芯片越来越大,DFT 也就成为必不可少的一步。DFT 通常要做 scan chain, mbist ,ATPG 等工作。

完成以上的工作后,就生成 nestlist 交给后端。

3. 后端设计

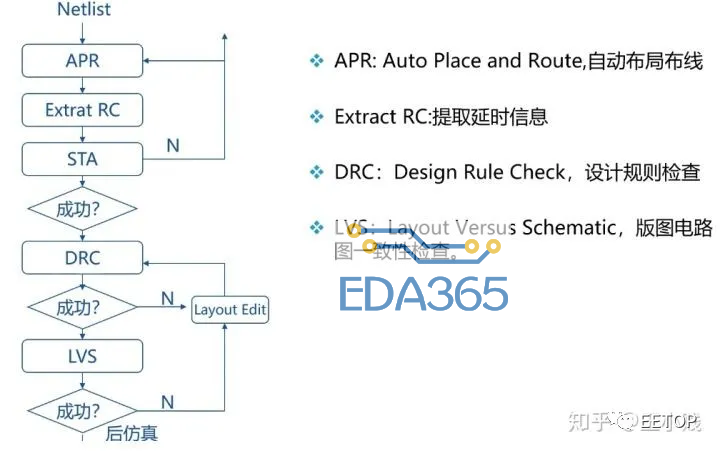

下图给出了后端设计的流程及主要工作。

Place & Route 一般由后端工程师来做,Physical Design Engineer.

后端里 DRC 就是要检查设计规则是否符合芯片制造商的要求,这样才能正确的生产芯片。

最后上一个全家福:

这里就不对每一步做具体的介绍了,因为内容实在太多,每一点都可以挖掘的很深入。

后端完成工作后,最终会生成 GDSII 格式的文件,交由芯片制造商流片。

二 . 每个流程使用的 EDA 工具

数字逻辑仿真工具:

cadence: Incisive

synopsys: VCS

mentor: QuestaSim

数字逻辑综合工具:

Cadence:Genus

Synopsis: design

Compiler (DC)

数字后端设计工具:

1. 自动布局布线工具

Cadence: Innovus

Synopsis: IC Compiler

2. 物理验证工具

Mentor: Calibre

Synopsis: Hercules

Cadence: Diva/dracula

APP下载

APP下载 登录

登录

热门文章

热门文章