IDT7132是一种高速2 K×16bit双端口静态RAM,且带片内总线仲裁电路,具有两组数据总线和地址总线,两组总线可以同时访问不同的存储器单元。当两组地址总线完全相同时,由片内总线仲裁逻辑向后访问的一方发出等待信号,使该方进入等待,待另一方访问结束后等待撤消,等待方继续访问这一地址。由于双端口RAM的特殊结构,使得双机可以方便、快速地进行数据交换,从而大大提高了多CPU系统的并行处理能力。

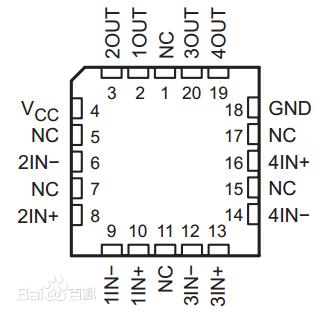

IDT7132的结构框图如图13.12所示。当引脚出现下降沿时选中DPRAM,即可通过控制或R/来访问内部存储单元。

IDT7312的核心部分是存储器阵列,用于数据存储,为左右两个端口公用。这样,位于两个端口的左右处理单元就可以共享一个存储器。当两个端口对双端口RAM存取时,IDT7312芯片设计有硬件功能输出,其工作原理如下。

· 当左右端口不对同一地址单元存取时,、均为高电平,可正常存储。

· 当左右端口对同一地址单元存取时,有一端口的为低电平,禁止数据的存取,此时,两个端口中哪个存取请求信号出现在前,则其对应的为高电平,允许存取,否则其对应的为高电平,禁止其写入数据。

IDT7312的时序与RAM的读写时序非常类似:当CPU选中DPRAM时,引脚出现下降沿,当控制线为高且R/为低时,CPU对内部存储单元进行写操作;而当控制线为低且R/为高时,CPU对内部存储单元进行读操作。IDT7312在非竞争情况下的读写控制字如表13-1所示。

图13.12 IDT7132结构框图

表13-1 IDT7132非竞争读写控制字

左或右端口 | 功 能 | |||

R/ | D7~D0 | — | ||

X | H | X | Z | 掉电模式 |

L | L | X | 数据输入 | 数据写入存储器 |

H | L | L | 数据输出 | 存储器中数据输出 |

H | L | H | Z | 输出呈高阻态 |

使用双端口RAM的关键是对竞争的处理。当外部CPU通过两个端口对双端口RAM内部的同一个存储单元进行操作(即两组地址总线完全相同)时,系统将出现竞争。为避免因竞争而导致的通信失败,设计者提出了各种解决方案,常见的有如下3种。

· 设置标志位。在开辟数据通信区的同时可通过软件方法在某个固定的存储单元设立标志位。这种方法要求两端CPU每次访问双端口RAM之前必须查询、测试和设置标志位,然后再根据标志位的状态决定是否可以访问数据区。

有的双端口本身就具有专用的一个或多个硬件标志锁存器和专门的测试和设置指令,可直接对标志位进行读写操作。这种方法通常用在多个处理器共享一个存储器块时。为了保证通信数据的完整性,在采用这种方法时往往要求每个处理器能对该存储器块进行互斥的存取。

· 软件查询引脚状态。双端口RAM必须具有解决两个处理器同时访问同一单元的竞争仲裁逻辑功能。当双方访问地址发生冲突时,竞争仲裁逻辑可用来决定哪个端口访问有效,同时取消无效端口的访问操作,并将禁止端口的信号置为低电平。因此信号可作为处理器等待逻辑的输入之一,即当为低电平时,让处理器进入等待状态,每次访问双端口RAM时,检查状态以判断是否发生竞争,只有为高时对双端口RAM的操作才有效。

· 利用硬件解决竞争。信号可以直接接至支持插入等待时序的CPU,如80C196的引脚,而无需软件支持。

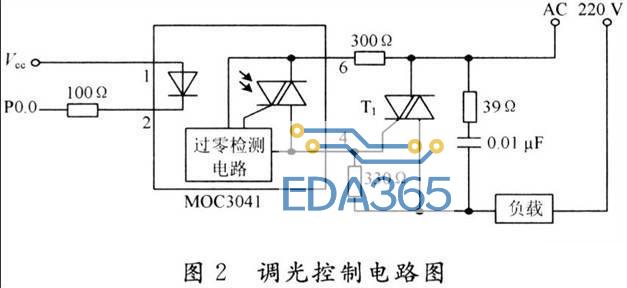

原理图如图13.13所示,由两个8051单片机和包括双端口RAM的单片机控制系统组成。两个单片机之间的通信是通过对双端口RAM的读写实现的。单片机对双端口RAM的访问与片外扩展RAM没有区别,例如,要对IDT7312的0x0单元进行操作,只需对片外地址0x7800进行操作即可;而要对IDT7312的0x0单元进行操作,只需对片外地址0x7801进行操作即可。

图13.13 8051与IDT7132组成的系统原理图

在本系统中,单片机U1将某些数据存入IDT7132,由U2将这些数据读入并处理,此时U1就可以去进行其他操作。显然,这种发放可以实现一定程度上的并行计算,在计算量较大的时候是比较可取的。

系统工作后,单片机U2连续读双端口RAM,先查询(P3.5)信号,若为高电平,说明不忙,则查询更新标志单元7800H。若7800H单元为#FFH,说明数据已经更新,单片机先把标志单元7800H置为#00H,再读入数据;若标志单元7800H为#00H,说明数据未更新,单片机U2再读IDT7132。单片机U2读双端口RAM的流程如图13.14(a)所示。单片机U1向IDT7132的写操作与此类似,首先把更新标志单元7800H置为#FFH,然后再向其中写入数据,如图13.14(b)所示。

图13.14 单片机读、写IDT7312的流程图

程序如例13-6所示,采用设置标志位和软件查询的方法解决竞争问题。

【例13-6】两片8051单片机通过双端口RAM IDT7132交换数据。IDT7312的第一个存储单元0x0作为更新标志,从0x1~0x0A的10个字节作为存储区,U1可以在满足条件时向此存储区写入数据,U2可以在满足条件时从此存储区读出数据。

U1的程序:

#include

typedef unsigned char uchar;

#define adr_flag ((uchar*)0x17800) //存放更新标志的地址

#define adr_store ((uchar*)0x17801) //存储区起始地址

sbit BL=P3^5; //P.5接BUSYL信号

void main(void)

{

uchar buf[10]; //存储从IDT7312中读取的数据

uchar i,temp;

while(1) //无限循环

{

buf[i]=*(adr_store+i); //读双端口RAM

if(!BL) break; //如果BUSYL信号为低,循环检测

temp=*adr_flag; //直到BUSYL信号变高

if(temp==0xff) break; //如果尚未更新,循环检测

else //如果已经更新

{

*adr_flag=0x0; //清除更新标志

for(i=0;i<=9;i++) //读取10个字节

buf[i]=*(adr_store+i);

}

}

}

U2的程序:

#include

typedef unsigned char uchar;

#define adr_flag ((uchar*)0x17800) //存放更新标志的地址

#define adr_store ((uchar*)0x17801) //存储区起始地址

sbit BR=P3^5; //P.5接BUSYR信号

void main(void)

{

uchar buf[10]; //将要写入的数据存放在buf[10]中

uchar i,temp;

while(1) //无限循环

{

*(adr_store+i)= buf[i]; //写双端口RAM

if(!BR) break; //如果BUSYR信号为低,循环检测

temp=*adr_flag; //直到BUSYR信号变高

if(temp==0) break; //若上次更新尚未被读取,循环检测

else //若已被读取

{

*adr_flag=0xff; //置更新标志

for(i=0;i<=9;i++) //写入10个字节

*(adr_store+i)=buf[i];

}

}

}

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多